# **I**HE 2<sup>ND</sup> EDITION **ELECTRONICS COMPANION** Devices and Circuits for

Physicists and Engineers

# A. C. FISCHER-CRIPPS

# THE 2ND EDITION ELECTRONICS COMPANION

This page intentionally left blank

# THE 2ND EDITION ELECTRONICS COMPANION

Devices and Circuits for Physicists and Engineers

# **ANTHONY C. FISCHER-CRIPPS**

Fischer-Cripps Laboratories Pty Ltd Sydney, Australia

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

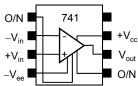

Cover design by Ray Cripps.

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2015 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20140709

International Standard Book Number-13: 978-1-4665-5267-8 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www. copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

This book is dedicated to Robert Winston Cheary.

This page intentionally left blank

## Contents

# Contents

| Preface      |                                    | xv |

|--------------|------------------------------------|----|

| 1. Electrici | ty                                 | 1  |

| 1.1          | Electricity                        | 2  |

| 1.2          | Electric Charge                    | 3  |

| 1.3          | Electric Flux                      | 4  |

| 1.4          | Conductors and Insulators          | 5  |

| 1.5          | Electric Current                   | 6  |

| 1.6          | Conventional Current               | 7  |

| 1.7          | Potential Difference               | 8  |

| 1.8          | Resistance                         | 9  |

| 1.9          | Resistivity                        | 10 |

| 1.10         | Variation of Resistance            | 11 |

| 1.11         | Resistor Circuits                  | 12 |

| 1.12         | Electromotive Force                | 13 |

| 1.13         | Capacitance                        | 14 |

| 1.14         | Capacitors                         | 15 |

| 1.15         | Energy Stored in a Capacitor       | 16 |

| 1.16         | Capacitor Circuits                 | 17 |

| 1.17         | Inductance                         | 18 |

| 1.18         | Inductors                          | 19 |

| 1.19         | Discharge and Stored Energy        | 20 |

| 1.20         | Review Questions                   | 21 |

| 2. DC Circu  | its                                | 23 |

| 2.1          | Superposition                      | 24 |

| 2.2          | Kirchhoff's Laws                   | 25 |

| 2.3          | Kirchhoff's Laws Example           | 26 |

| 2.4          | Thevenin's Theorem                 | 27 |

| 2.5          | Thevenin's Theorem Example         | 28 |

| 2.6          | Norton's Theorem                   | 29 |

| 2.7          | Norton's Theorem Example           | 30 |

| 2.8          | Equivalence of Norton and Thevenin | 31 |

| 2.9          | Maximum Power Transfer             | 32 |

| 2.10         | Review Questions                   | 33 |

| 3. AC Circu | uits                               | 35 |

|-------------|------------------------------------|----|

| 3.1         | AC Voltage                         | 36 |

| 3.2         | Resistance                         | 37 |

| 3.3         | rms Voltage and Current            | 38 |

| 3.4         | Capacitive Reactance               | 39 |

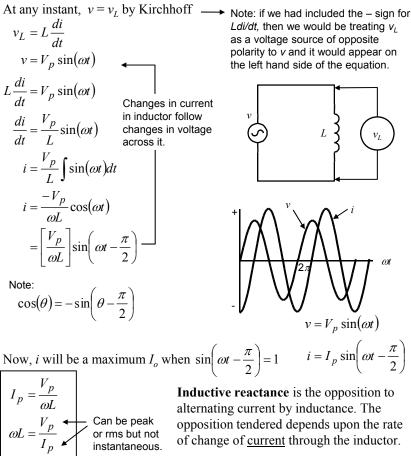

| 3.5         | Inductive Reactance                | 40 |

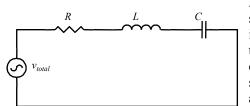

| 3.6         | LCR series Circuit                 | 41 |

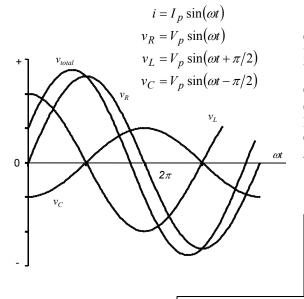

| 3.7         | LCR Circuit – Peak and rms Voltage | 42 |

| 3.8         | Impedance                          | 43 |

| 3.9         | Low-Pass Filter                    | 44 |

| 3.10        | High-Pass Filter                   |    |

| 3.11        | Complex Impedance (series)         | 46 |

| 3.12        | Resonance (series)                 | 47 |

| 3.13        | Impedance (parallel)               | 48 |

| 3.14        | Impedances (series and parallel)   | 40 |

| 3.15        | Impedances (example)               | 50 |

| 3.16        | AC Circuits                        | 51 |

| 3.17        | AC Circuits (example)              | 52 |

| 3.18        | Filters Complex Form               | 53 |

| 3.19        | Signal Generator and Oscilloscope  | 54 |

| 3.20        | AC Bridge                          | 55 |

| 3.21        | Review Questions                   | 56 |

| 1 Diadas    |                                    | 50 |

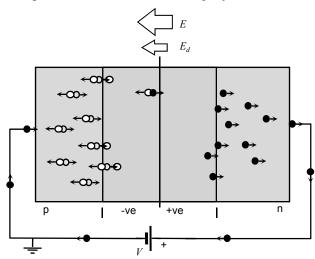

| 4.1         | Semiconductors                     |    |

| 4.1         | P- and N-Type Semiconductors       |    |

| 4.2         | Response in an Electric Field      |    |

| 4.4         | P-N Junction                       |    |

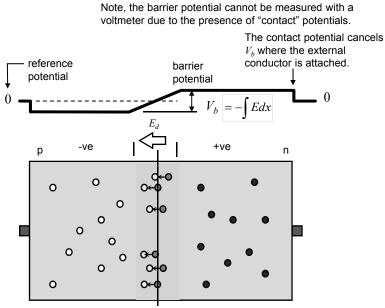

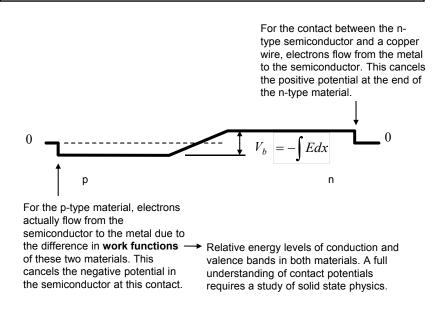

| 4.5         | Contact Potential                  |    |

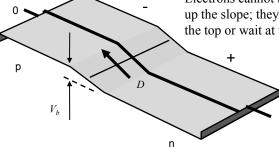

| 4.6         | Potential Diagram                  |    |

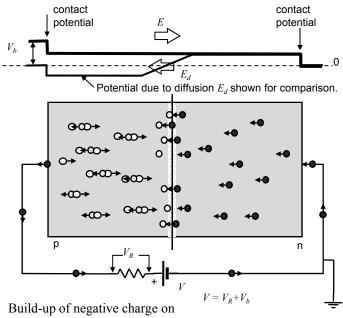

| 4.7         | Forward Bias                       |    |

| 4.8         | Reverse Bias                       |    |

| 4.9         | Potential Diagrams                 | -  |

| 4.10        | Diode                              |    |

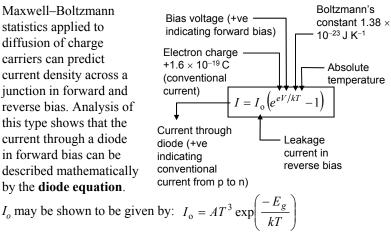

| 4.11        | Diode Equation                     |    |

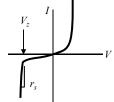

| 4.12        | Reverse Bias Breakdown             |    |

| 7.12        |                                    |    |

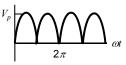

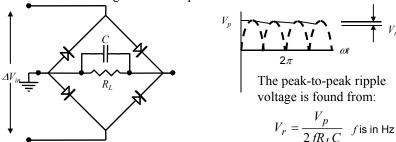

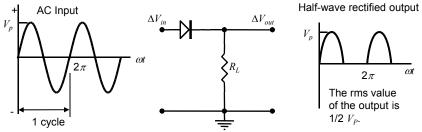

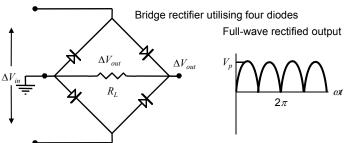

|    | 4.13   | Rectification                              | 72 |

|----|--------|--------------------------------------------|----|

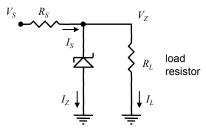

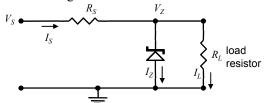

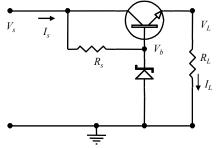

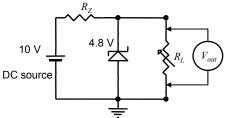

|    | 4.14   | Regulation                                 | 73 |

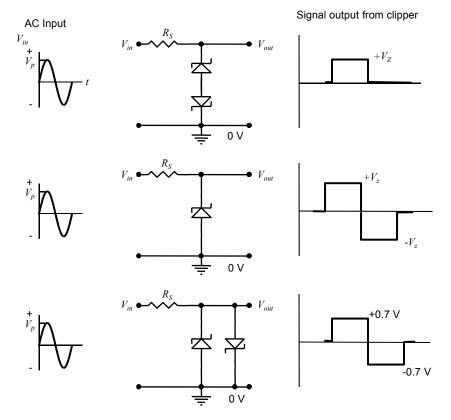

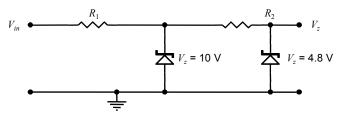

|    | 4.15   | Clipper                                    | 74 |

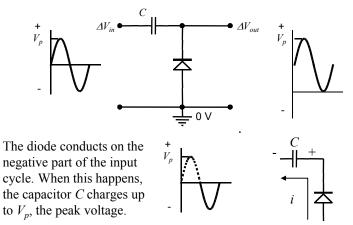

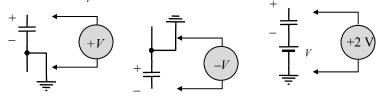

|    | 4.16   | Clamp                                      | 75 |

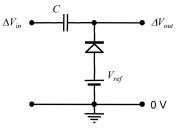

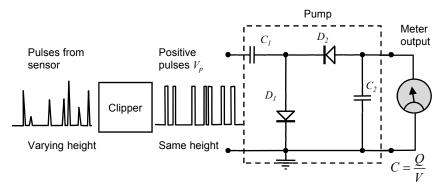

|    | 4.17   | Pump                                       | 76 |

|    | 4.18   | Photodiode                                 | 77 |

|    | 4.19   | LED                                        | 78 |

|    | 4.20   | Review Questions                           | 79 |

|    |        |                                            |    |

| 5. | •      | unction Transistor                         |    |

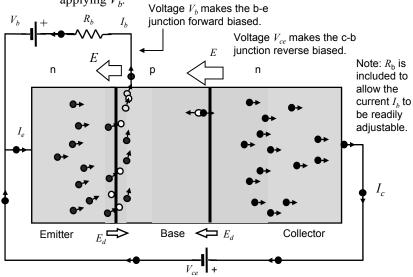

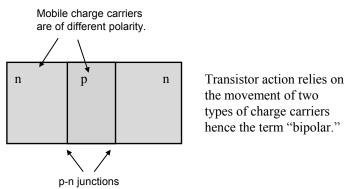

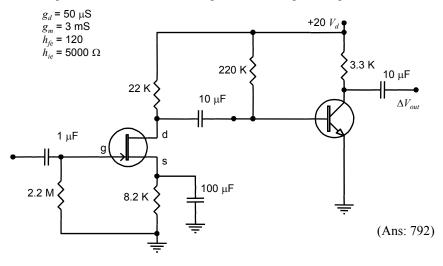

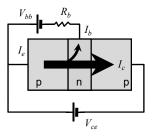

|    | 5.1    | Bipolar Junction Transistor – Construction |    |

|    | 5.2    | Bipolar Junction Transistor – Operation    |    |

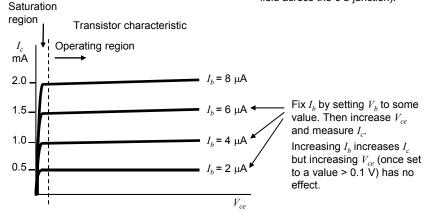

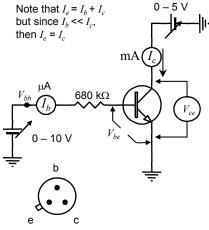

|    | 5.3    | Transistor Characteristic                  |    |

|    | 5.4    | Load Line                                  |    |

|    | 5.5    | Saturation                                 |    |

|    | 5.6    | Transistor Switch                          |    |

|    | 5.7    | Simple Bias                                |    |

|    | 5.8    | Emitter Bias                               | -  |

|    | 5.9    | Stabilisation                              |    |

|    | 5.10   | Voltage Amplifier                          | 93 |

|    | 5.11   | Bias                                       |    |

|    | 5.12   | Review Questions                           | 95 |

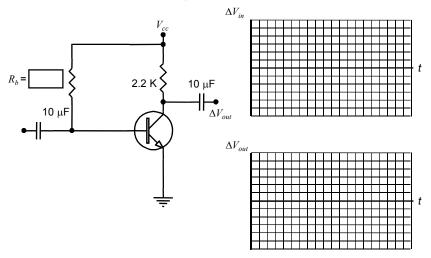

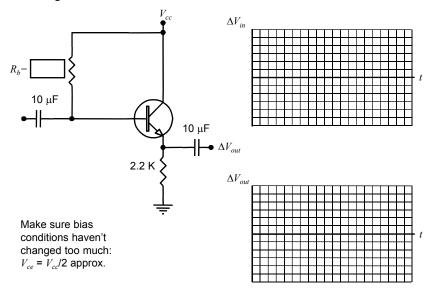

| 6. | Common | e Emitter Amplifier                        | 97 |

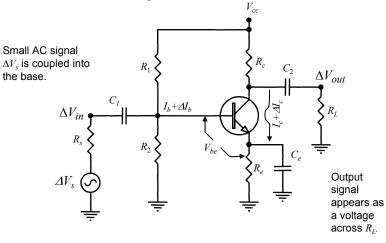

|    | 6.1    | Coupling Capacitors                        |    |

|    | 6.2    | Bypass Capacitor                           |    |

|    | 6.3    | Voltage Amplifier                          |    |

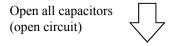

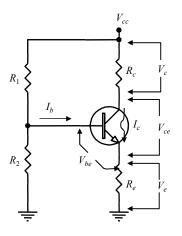

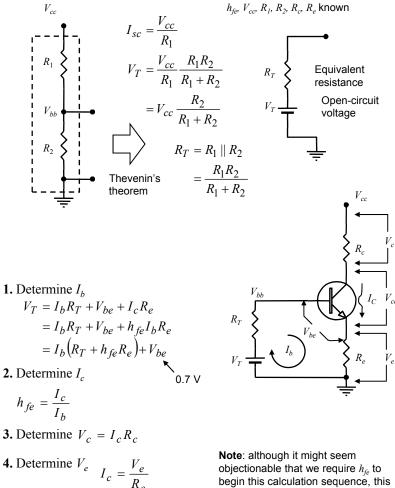

|    | 6.4    | DC Analysis                                |    |

|    | 6.5    | AC Analysis                                |    |

|    | 6.6    | ,<br>Input and Output Resistances – AC     |    |

|    | 6.7    | AC Voltage Gain                            |    |

|    | 6.8    | Bypass Capacitor                           |    |

|    | 6.9    | Amplifier Design                           |    |

|    | 6.10   | Amplifier Design – Input Resistance        |    |

|    | 6.11   | Amplifier Design – $V_{cc}$                |    |

|    | 6.12   | Amplifier Design – $V_{ce}$                |    |

|    |        |                                            |    |

| 6.13      | Amplifier Design – $R_T$                                                                                                                                                                                                                                                                     | 113                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 6.14      | Amplifier Design – R <sub>1</sub>                                                                                                                                                                                                                                                            | 114                                                                                         |

| 6.15      | Review Questions                                                                                                                                                                                                                                                                             | 115                                                                                         |

|           |                                                                                                                                                                                                                                                                                              |                                                                                             |

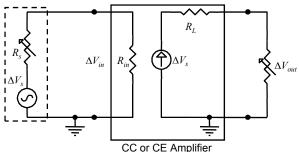

| nput/Ou   | Itput Impedance                                                                                                                                                                                                                                                                              | 119                                                                                         |

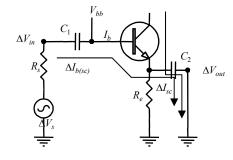

| 7.1       | CE Input Impedance                                                                                                                                                                                                                                                                           | 120                                                                                         |

| 7.2       | CE Output Impedance                                                                                                                                                                                                                                                                          | 121                                                                                         |

| 7.3       | AC Voltage Gain                                                                                                                                                                                                                                                                              | 123                                                                                         |

| 7.4       | Impedance Matching                                                                                                                                                                                                                                                                           | 124                                                                                         |

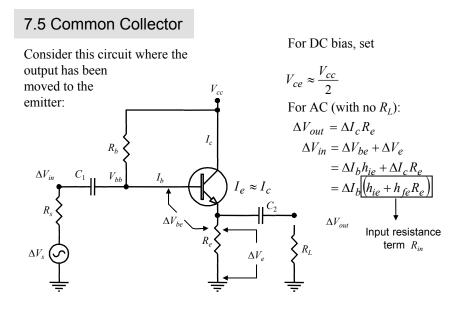

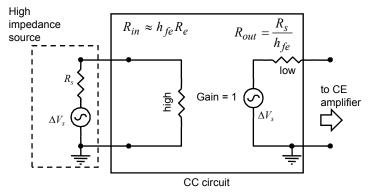

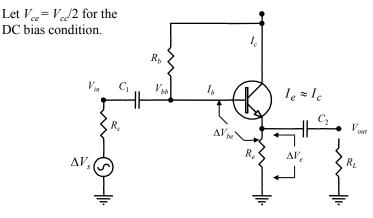

| 7.5       | Common Collector                                                                                                                                                                                                                                                                             | 125                                                                                         |

| 7.6       | CC Output Impedance                                                                                                                                                                                                                                                                          | 126                                                                                         |

| 7.7       | CC Input/Output Impedance                                                                                                                                                                                                                                                                    | 127                                                                                         |

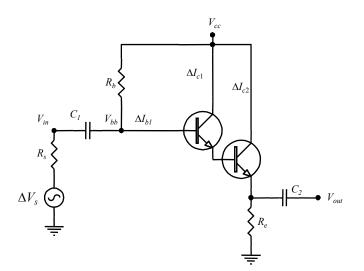

| 7.8       | Darlington Pair                                                                                                                                                                                                                                                                              | 128                                                                                         |

| 7.9       | Review Questions                                                                                                                                                                                                                                                                             | 129                                                                                         |

|           |                                                                                                                                                                                                                                                                                              |                                                                                             |

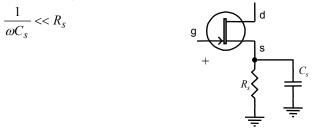

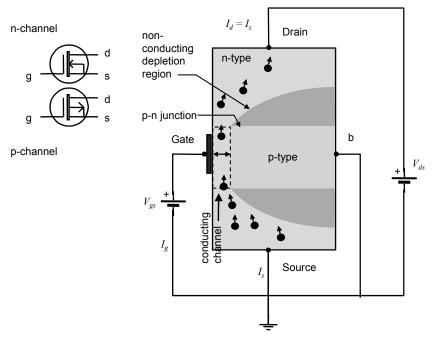

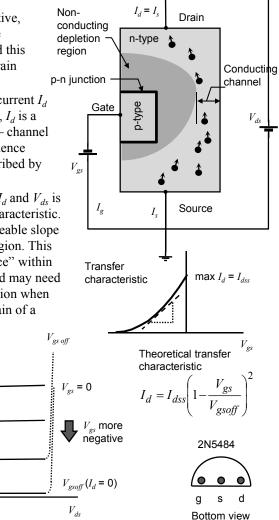

| ield Effe |                                                                                                                                                                                                                                                                                              |                                                                                             |

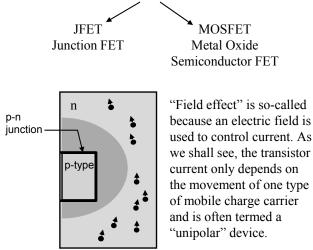

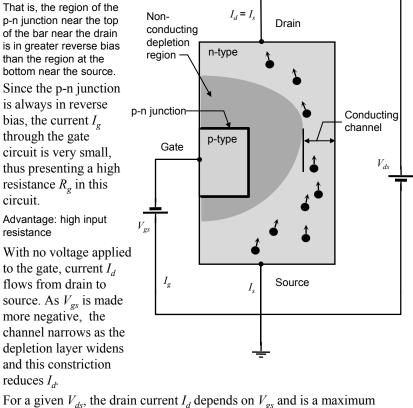

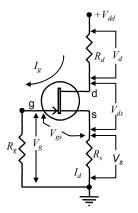

| 8.1       | Field Effect Transistor                                                                                                                                                                                                                                                                      | 132                                                                                         |

| 8.2       |                                                                                                                                                                                                                                                                                              |                                                                                             |

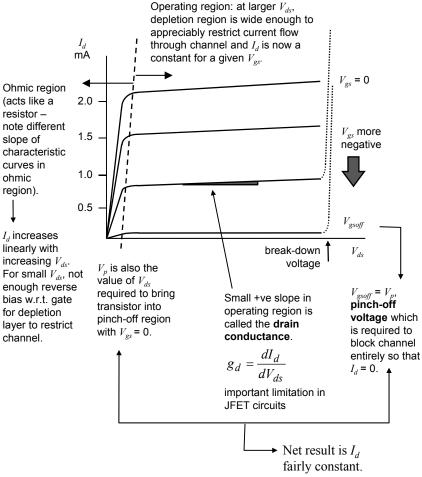

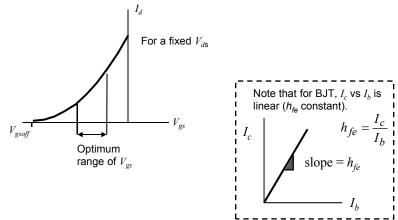

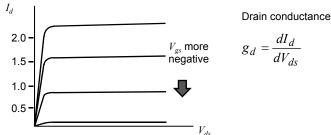

| 8.3       | JFET Characteristic                                                                                                                                                                                                                                                                          | 134                                                                                         |

| 8.4       | JFET Drain Curve                                                                                                                                                                                                                                                                             | 135                                                                                         |

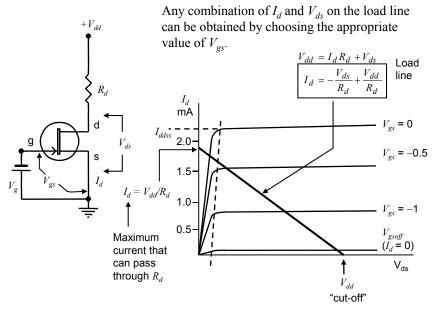

| 8.5       | JFET Load Line                                                                                                                                                                                                                                                                               | 136                                                                                         |

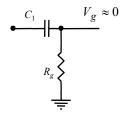

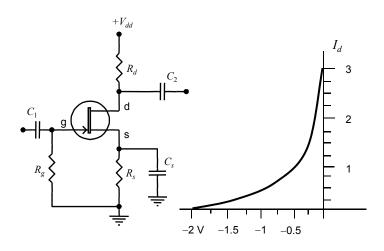

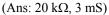

| 8.6       | JFET Biasing                                                                                                                                                                                                                                                                                 | 137                                                                                         |

| 8.7       |                                                                                                                                                                                                                                                                                              |                                                                                             |

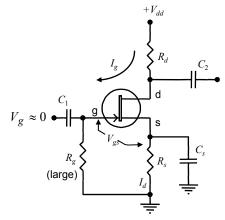

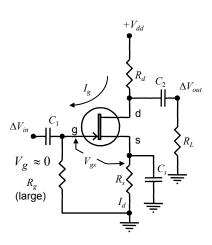

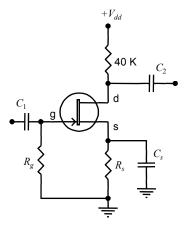

| 8.8       | Common Source Amplifier                                                                                                                                                                                                                                                                      | 139                                                                                         |

| 8.9       | Drain Conductance g <sub>d</sub>                                                                                                                                                                                                                                                             | 140                                                                                         |

| 8.10      | Amplifier Design                                                                                                                                                                                                                                                                             | 141                                                                                         |

| 8.11      |                                                                                                                                                                                                                                                                                              |                                                                                             |

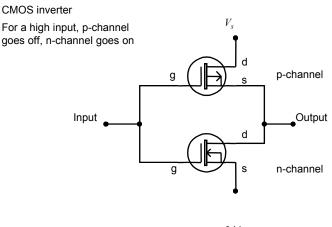

| 8.12      | MOSFETS                                                                                                                                                                                                                                                                                      | 143                                                                                         |

| 8.13      | CMOS                                                                                                                                                                                                                                                                                         | 144                                                                                         |

| 8.14      | Review Questions                                                                                                                                                                                                                                                                             | 145                                                                                         |

|           |                                                                                                                                                                                                                                                                                              |                                                                                             |

| -         |                                                                                                                                                                                                                                                                                              |                                                                                             |

| 9.1       | -                                                                                                                                                                                                                                                                                            |                                                                                             |

| 9.2       |                                                                                                                                                                                                                                                                                              |                                                                                             |

| 9.3       | ·                                                                                                                                                                                                                                                                                            |                                                                                             |

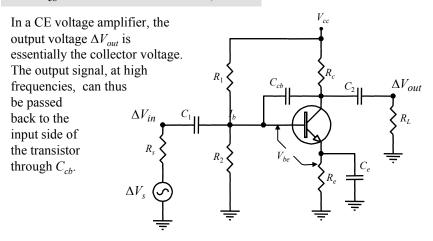

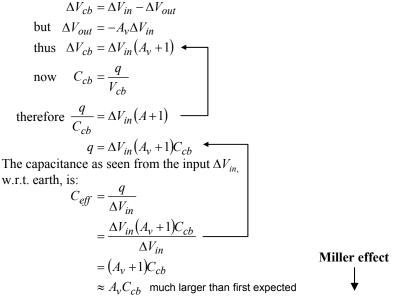

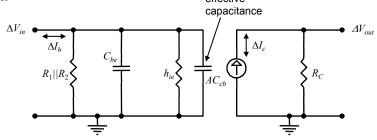

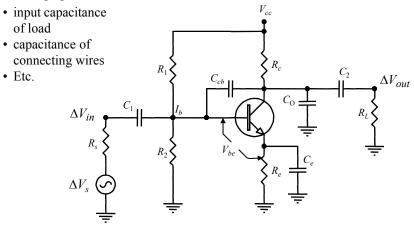

| 9.4       | Miller Effect                                                                                                                                                                                                                                                                                | 151                                                                                         |

|           | 6.14<br>6.15<br>nput/Ou<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>ield Effe<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.10<br>8.11<br>8.12<br>8.13<br>8.11<br>8.12<br>8.13<br>8.14<br>119,2<br>9.1<br>9.2<br>9.3 | 6.14       Amplifier Design $-R_1$ 6.15       Review Questions <b>nput/Output Impedance</b> |

| 9.5        | Output Capacitance                | 152 |

|------------|-----------------------------------|-----|

| 9.6        | Amplification at High Frequencies | 153 |

| 9.7        | Review Questions                  | 154 |

| 10. Power  | · Amplifiers                      | 155 |

| 10.1       | Amplifier Power Output            | 156 |

| 10.2       | Class A Amplifier                 | 157 |

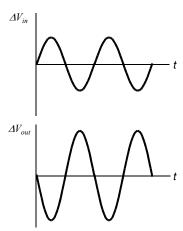

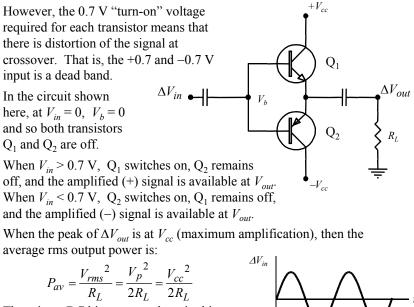

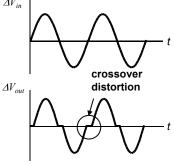

| 10.3       | Class B Amplifier                 | 158 |

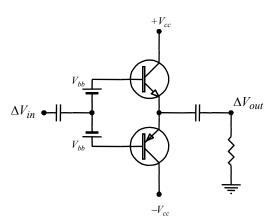

| 10.4       | Class AB Amplifier                | 159 |

| 10.5       | Class AB Diode Biasing            | 160 |

| 11. Transi | ents                              | 161 |

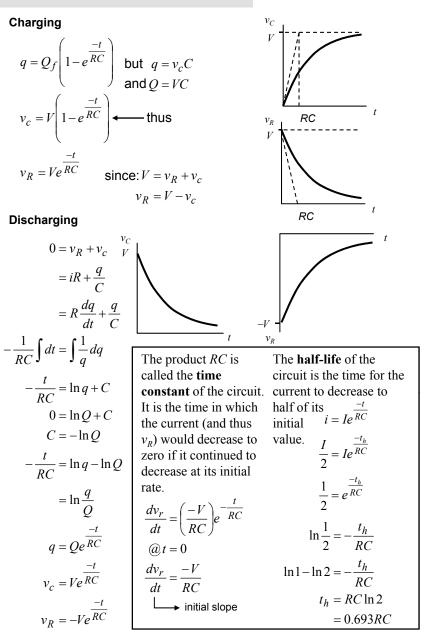

| 11.1       | R-C Circuit Analysis              | 162 |

| 11.2       | Time Constant and Half-Life       | 163 |

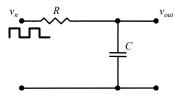

| 11.3       | R-C Low-Pass Filter               | 164 |

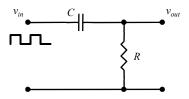

| 11.4       | R-C High-Pass Filter              | 165 |

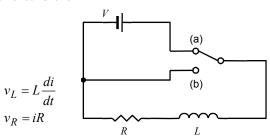

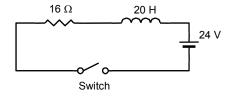

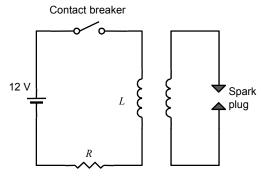

| 11.5       | R-L Circuits                      | 166 |

| 11.6       | R-L Circuits                      | 167 |

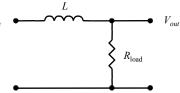

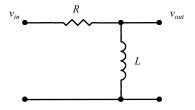

| 11.7       | R-L Filter Circuits               | 168 |

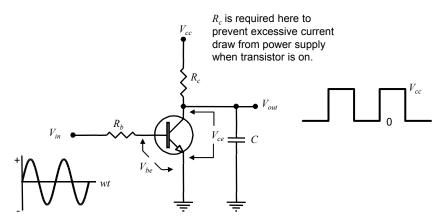

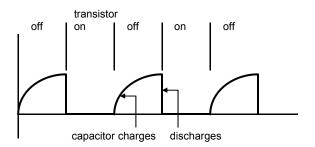

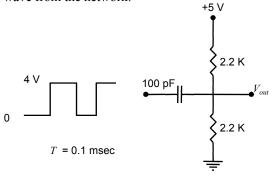

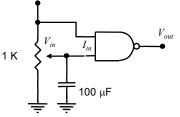

| 11.8       | Transistor Circuits               | 169 |

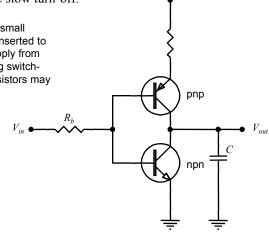

| 11.9       | Active Pull-Up                    | 170 |

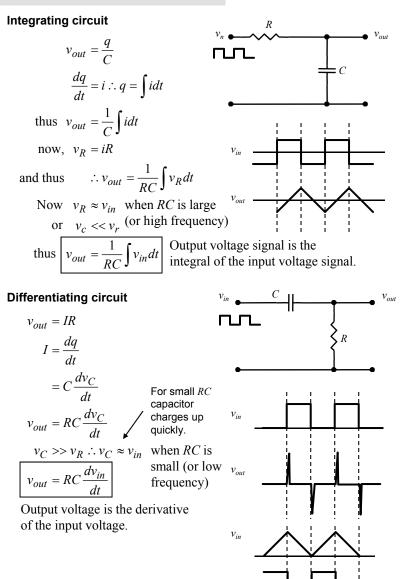

| 11.10      | Integrator/Differentiator         | 171 |

| 11.11      | Review Questions                  | 172 |

| 12. Digita | l Electronics                     | 175 |

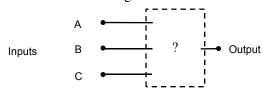

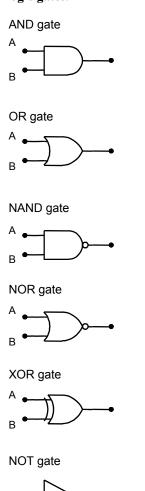

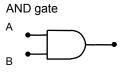

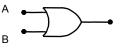

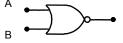

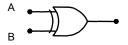

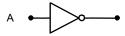

| 12.1       | Digital Logic                     | 176 |

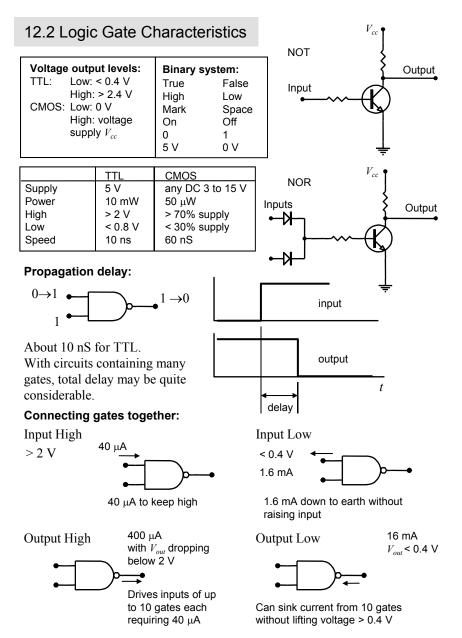

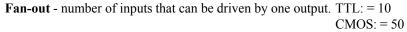

| 12.2       | Logic Gate Characteristics        | 177 |

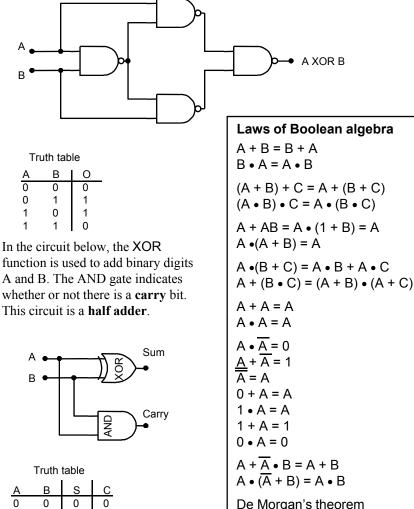

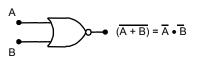

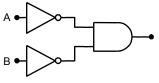

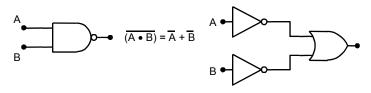

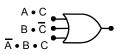

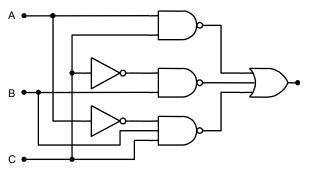

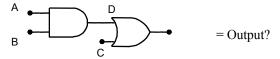

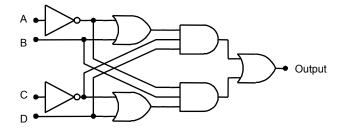

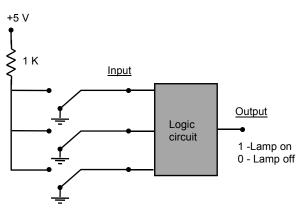

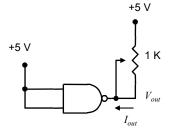

| 12.3       | Digital Logic Circuits            | 178 |

| 12.4       | Boolean Logic Examples            | 179 |

| 12.5       | Logic Circuit Analysis            | 180 |

| 12.6       | Karnaugh Map                      | 181 |

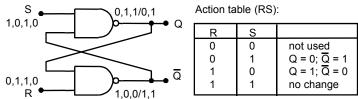

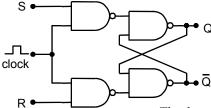

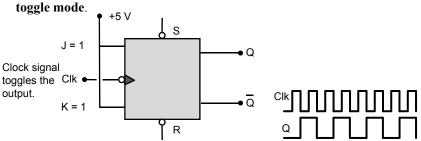

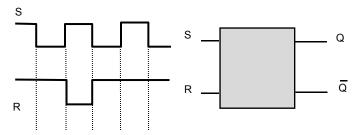

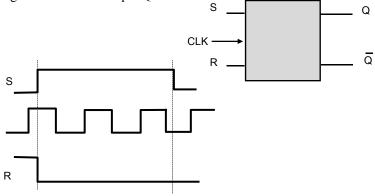

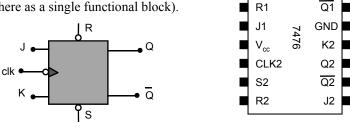

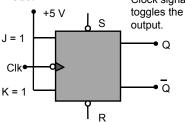

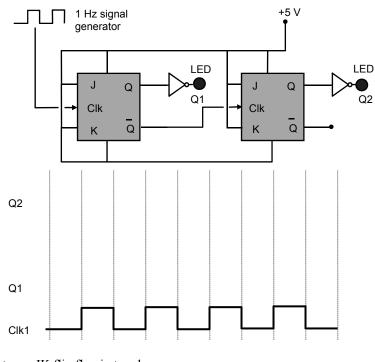

| 12.7       | Flip-Flops                        | 183 |

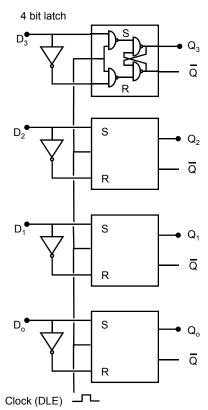

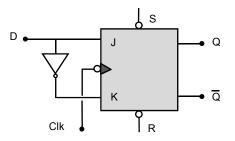

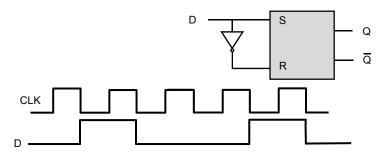

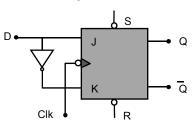

| 12.8       | D-Latch                           |     |

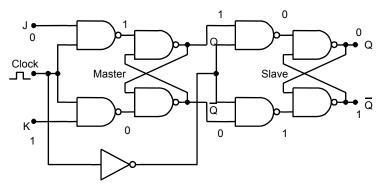

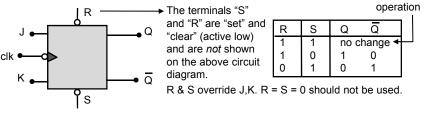

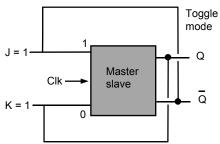

| 12.9       | J-K Master-Slave Flip-Flop        | 185 |

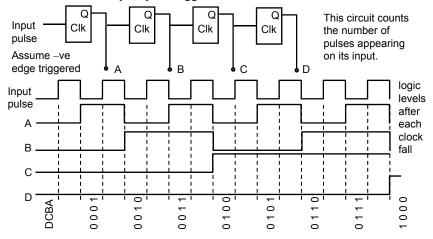

| 12.10      | J-K Flip-Flop Examples            | 186 |

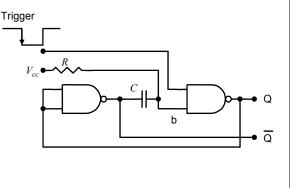

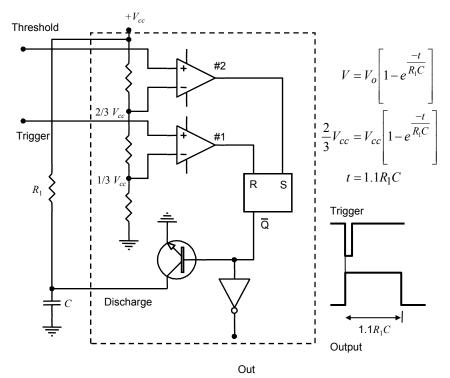

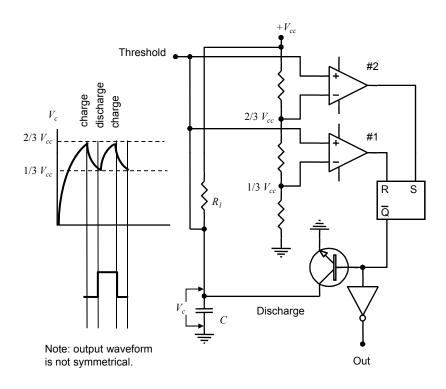

| 12.11      | Monostable Multivibrator          |     |

|    | 12.12   | 555 Timer                 | 188 |

|----|---------|---------------------------|-----|

|    | 12.13   | Review Questions          | 190 |

|    |         |                           |     |

| 13 | Operati | onal Amplifiers           | 193 |

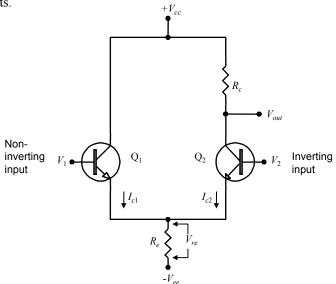

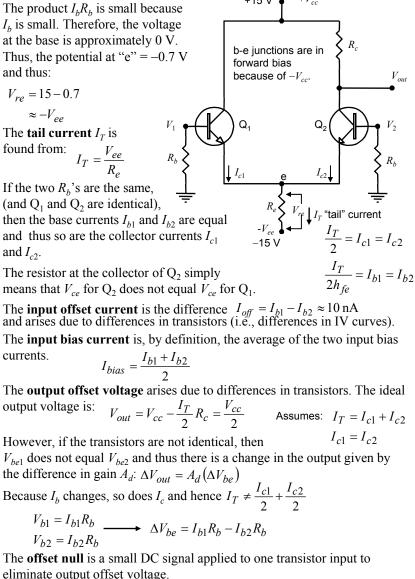

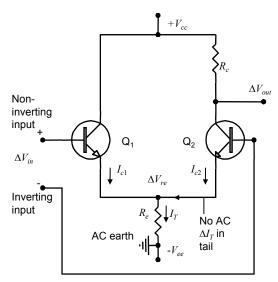

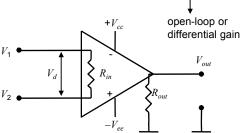

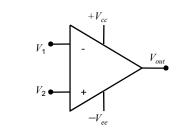

|    | 13.1    | Differential Amplifier    | 194 |

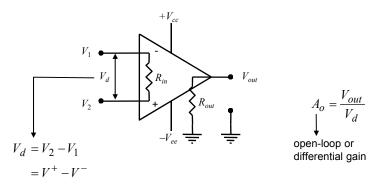

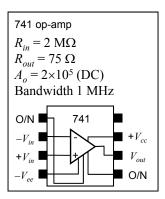

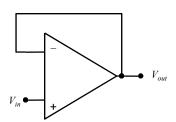

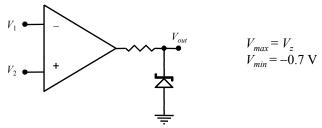

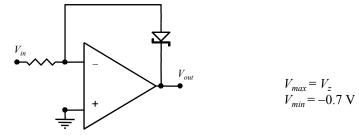

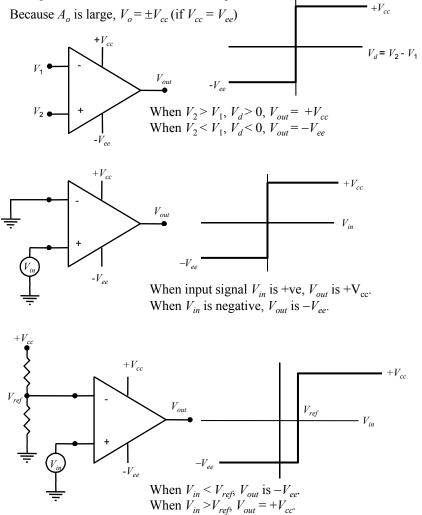

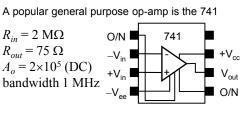

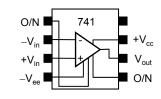

|    | 13.2    | Operational Amplifier     | 197 |

|    | 13.3    | Feedback                  | 198 |

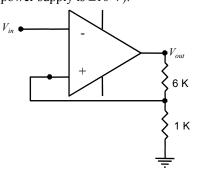

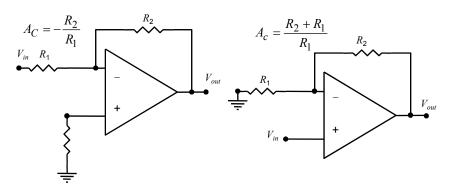

|    | 13.4    | Inverting Amplifier       | 199 |

|    | 13.5    | Non-Inverting Amplifier   | 200 |

|    | 13.6    | Offset                    | 201 |

|    | 13.7    | Op-Amp Bias               | 202 |

|    | 13.8    | Common Mode Gain          | 203 |

|    | 13.9    | Op-Amp Applications       | 204 |

|    | 13.10   | Operational Adder         | 205 |

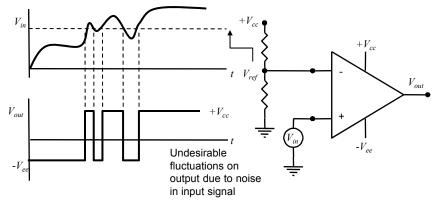

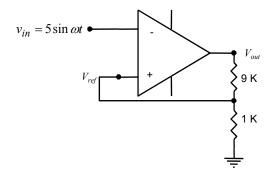

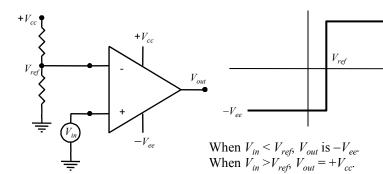

|    | 13.11   | Comparator                | 206 |

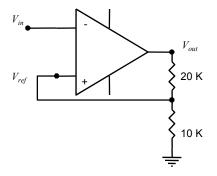

|    | 13.12   | Schmitt Trigger           | 207 |

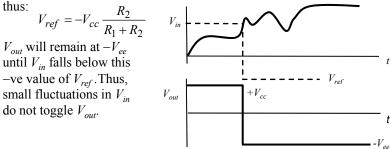

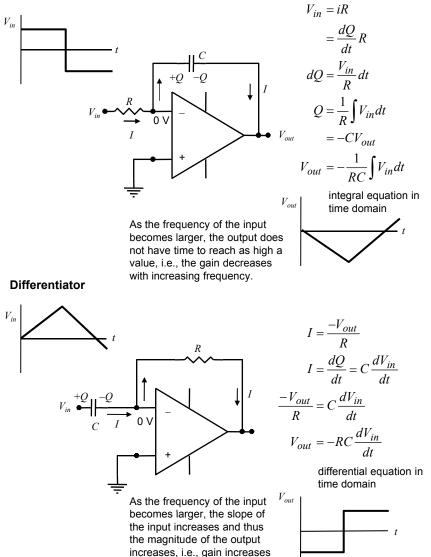

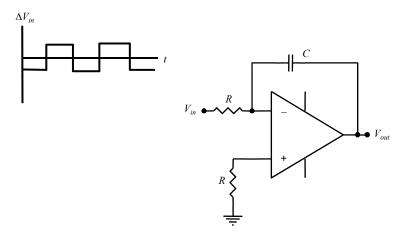

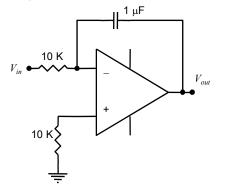

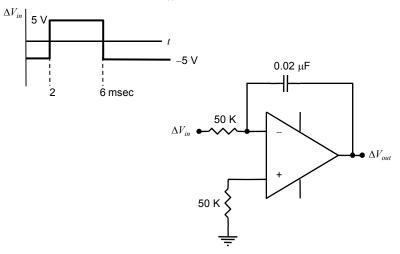

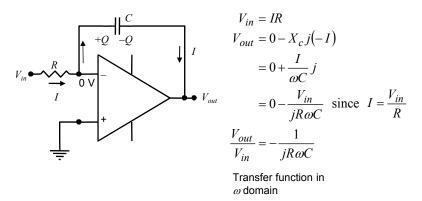

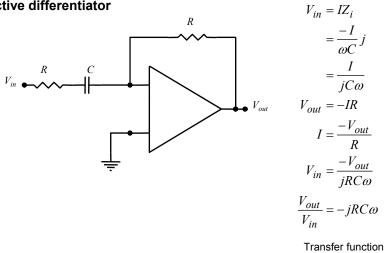

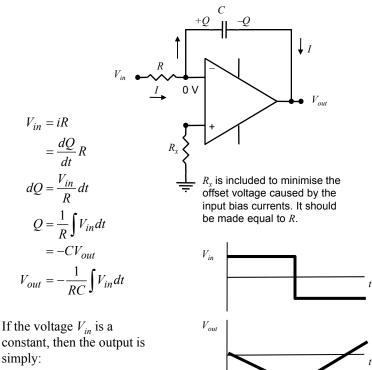

|    | 13.13   | Integrator/Differentiator | 208 |

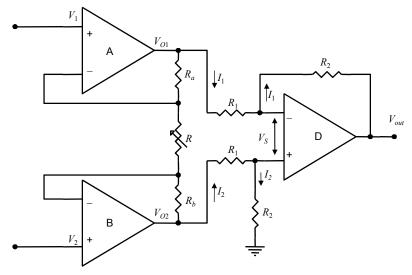

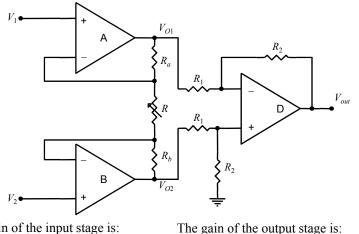

|    | 13.14   | Instrumentation Amplifier | 209 |

|    | 13.15   | Audio Amplifier           | 210 |

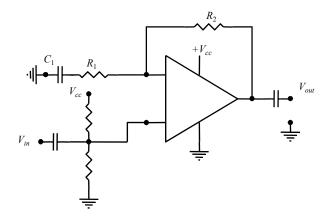

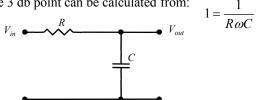

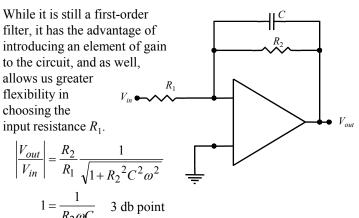

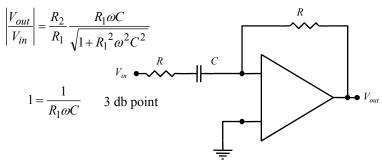

|    | 13.16   | Active Filter (1st-order) | 211 |

|    | 13.17   | Active Filter (2nd-order) | 212 |

|    | 13.18   | Review Questions          | 213 |

|    |         |                           |     |

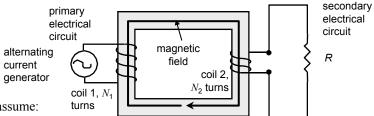

| 14 | Transfo | rmers                     | 217 |

|    | 14.1    | Transformers              | 218 |

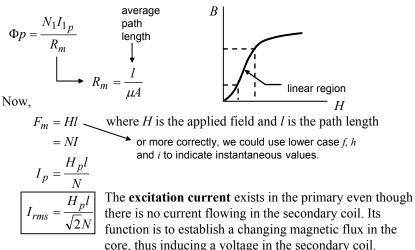

|    | 14.2    | Transformer Equations     | 219 |

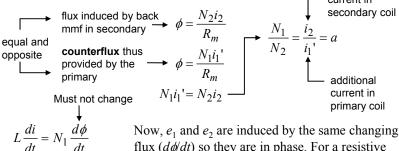

|    | 14.3    | Transformer Action        | 220 |

|    | 14.4    | Transformer Impedance     | 221 |

|    | 14.5    | Load Component of Primary | 222 |

|    | 14.6    | Reflected Impedance       | 223 |

|    | 14.7    | Real Transformers         | 224 |

|    | 14.8    | Transformer Tests         | 225 |

|    | 14.9    | Transformer Efficiency    | 226 |

xii

| 15 | . Power S | Suppliers                    | .227 |

|----|-----------|------------------------------|------|

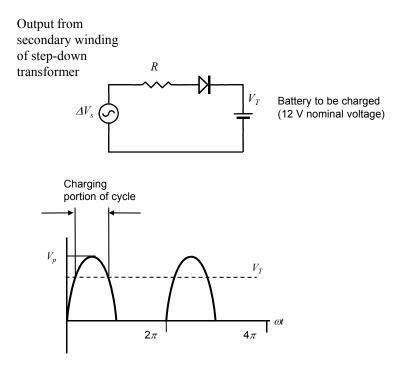

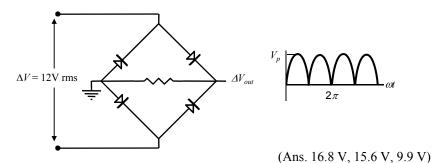

|    | 15.1      | Rectification                | .228 |

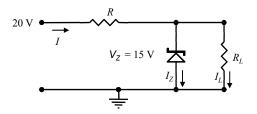

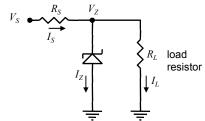

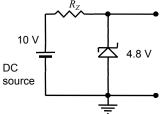

|    | 15.2      | Regulation                   | .229 |

|    | 15.3      | Load and Line Regulation     | .230 |

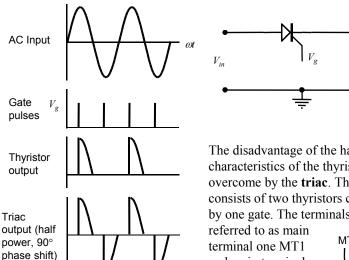

|    | 15.4      | Thyristor and Triac          | .231 |

|    | 15.5      | Review Questions             | .232 |

| 16 | . Instrum | nentation                    | .233 |

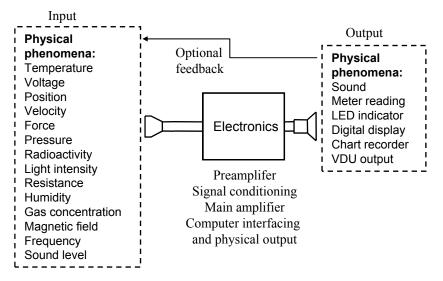

|    | 16.1      | Instrumentation              | .234 |

|    | 16.2      | Transducers                  |      |

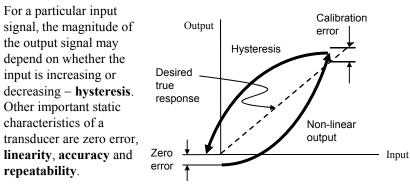

|    | 16.3      | Transducer Characteristics   | .236 |

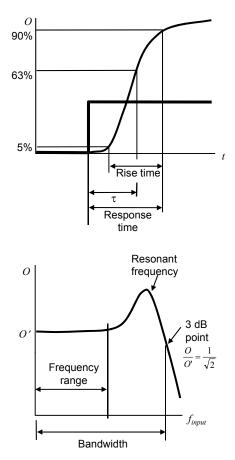

|    | 16.4      | Transducer Dynamic Response  | .237 |

|    | 16.5      | Noise                        | .238 |

|    | 16.6      | Transfer Function            | .239 |

|    | 16.7      | Integrator/Differentiator    | .240 |

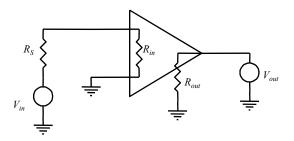

|    | 16.8      | Amplification                | .241 |

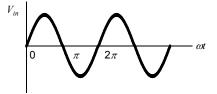

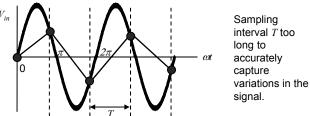

|    | 16.9      | Sampling                     | .242 |

|    | 16.10     | Digital Resolution           | .243 |

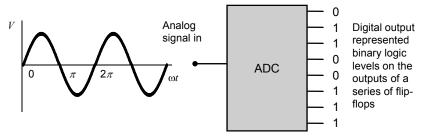

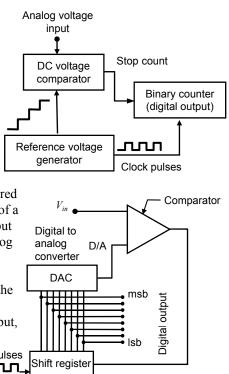

|    | 16.11     | Analog to Digital Conversion | .244 |

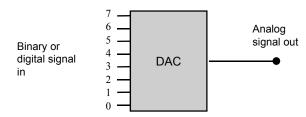

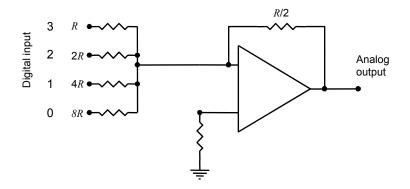

|    | 16.12     | Digital to Analog Conversion | .245 |

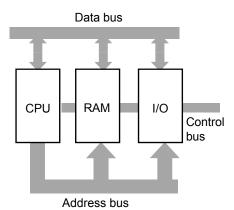

|    | 16.13     | Computer Architecture        | .246 |

|    | 16.14     | Ports                        | .247 |

|    | 16.15     | Review Questions             | .248 |

| 17 | . Laborat | ory                          | .250 |

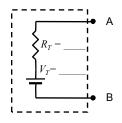

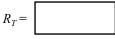

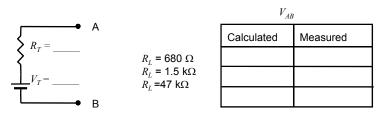

|    | 17.1      | Thevenin's Theorem           | .251 |

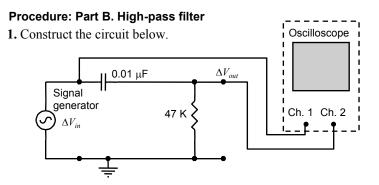

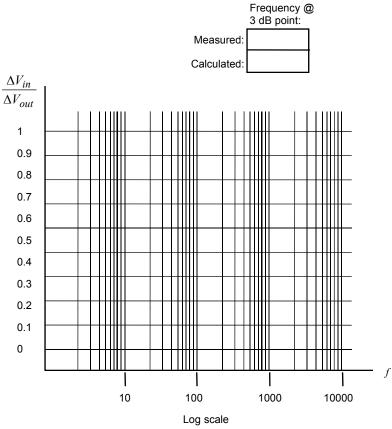

|    | 17.2      | AC Circuits                  | .255 |

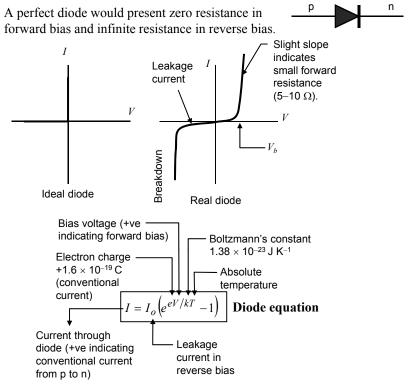

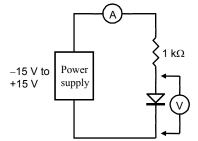

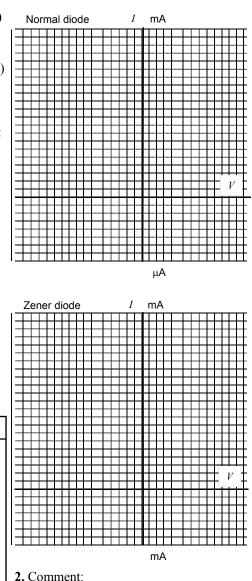

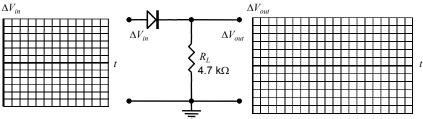

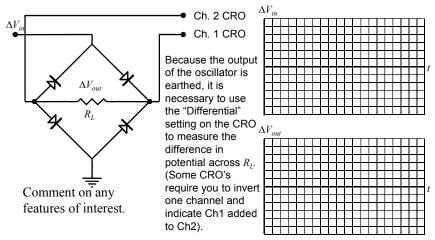

|    | 17.3      | Diode Characteristics        | .258 |

|    | 17.4      | Energy Gap                   | .261 |

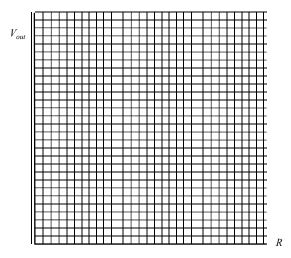

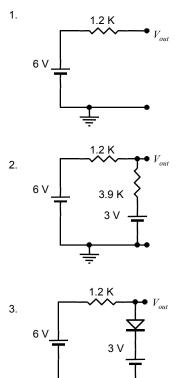

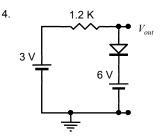

|    | 17.5      | Diode Circuits               | .263 |

|    | 17.6      | Clipper and Clamps           | .267 |

|    | 17.7      | Transistor Characteristics   | .269 |

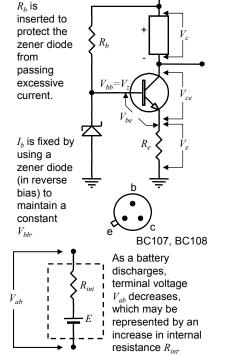

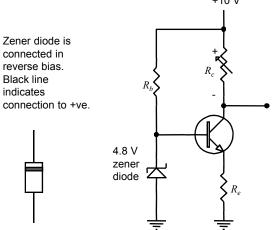

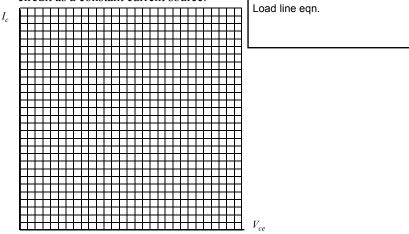

|    | 17.8      | NiCad Battery Charger        | .272 |

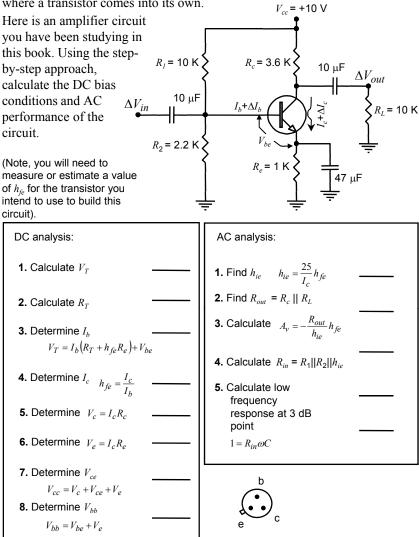

|    | 17.9      | Transistor Amplifier         | .276 |

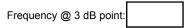

|    | 17.10     | Amplifier Design             | .279 |

| 17.11 | Impedance Matching      | 281 |

|-------|-------------------------|-----|

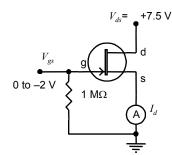

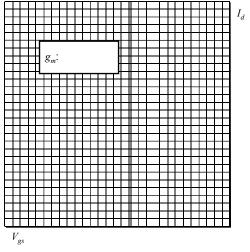

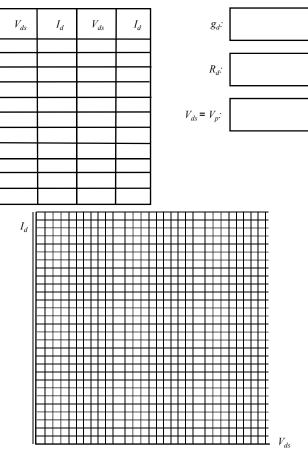

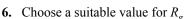

| 17.12 | FET                     | 284 |

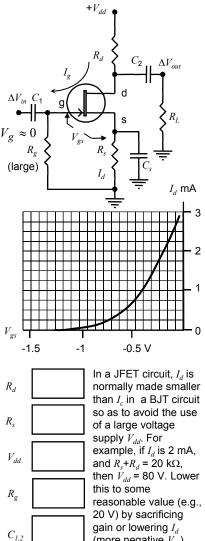

| 17.13 | Common Source Amplifier | 287 |

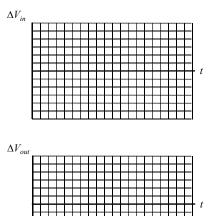

| 17.14 | Logic Gates             | 289 |

| 17.15 | Logic Circuits          | 292 |

| 17.16 | Counters and Flip-Flops | 294 |

| 17.17 | Op-Amps                 | 296 |

| 17.18 | Comparator              | 298 |

| 17.19 | Integrator              |     |

| 17.20 | Component Values        | 302 |

| Index |                         |     |

## Preface

This book is designed to help you understand the basic principles of electronics. The combination of succinct, but detailed explanations, review questions, and laboratory experiments work together to provide a consistent and logical account of the way in which basic electronics circuits are designed and how they work. The book arose out of a series of lectures that I attended as a student, and then later in life, as the lecturer. I am indebted to the late Robert Cheary, who presented this course for many years at the University of Technology, Sydney. I also express my appreciation to Walter Kalceff and Les Kirkup, my co-presenters, and Anthony Wong, who assisted me in the laboratory with many generations of enthusiastic students.

This second edition falls under the auspices of Taylor & Francis. I thank Tom Spicer and John Navas for their sponsorship of the first edition at the Institute of Physics Publishing, and to Francesca McGowan and the publication team at Taylor & Francis for their continued support and very professional approach to the whole publication process.

I hope that you will find this book a useful companion in your study of electronics.

Tony Fischer-Cripps, Killarney Heights, Australia This page intentionally left blank

| Summary                                       |                                    |                                                    |                         |

|-----------------------------------------------|------------------------------------|----------------------------------------------------|-------------------------|

| $F = k \frac{q_1 q_2}{d^2}$                   | Force between<br>two charges where | $k = \frac{1}{4}$                                  |                         |

| $F = q_1 E$                                   | Force on a charge a field          | in $4\pi \varepsilon_{o}$                          |                         |

| $E = 4\pi k \frac{Q}{A}$                      | Electric field - point<br>charge   | t                                                  |                         |

| $\overline{E} = k \frac{q\hat{r}}{r^2}$       | Electric field - point<br>charge   | t                                                  |                         |

| $\phi = EA$                                   | Electric flux                      |                                                    |                         |

| $I = A(q_1n_1v_1 +$                           | $+(-q_2)n_2(-v_2)\Big)$            |                                                    |                         |

| $i = \frac{dq}{dt}$                           | Electric current                   |                                                    |                         |

| $\frac{W}{q} = Ed$                            | Electric potential                 |                                                    |                         |

| $\frac{V}{I} = R$                             | Ohm's law                          | $U = \frac{1}{2}CV^2$                              | Energy -<br>capacitor   |

| $P = VI = I^2 R$                              | Power - resistor                   | $U = \frac{1}{2}LI^2$                              | Energy -<br>inductor    |

| $R = \rho \frac{1}{A}$                        |                                    | $R_{AB} = R_1 + R_2$                               | Resistors -<br>series   |

| $C = \frac{Q}{V} = \varepsilon_0 \frac{A}{d}$ |                                    | $\frac{1}{R_{AB}} = \frac{1}{R_1} + \frac{1}{R_2}$ | Resistors -<br>parallel |

| $L = \mu_0 A \frac{N^2}{1}$                   | Inductance                         | $R_{AB} = \frac{R_1 R_2}{R_1 + R_2}$               |                         |

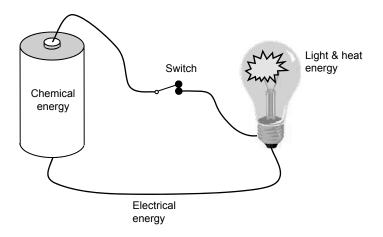

Consider a circuit in which a battery is connected to a light bulb through a switch.

In this simple electrical system, **chemical energy** is converted into **electrical energy** in the battery. The electrical energy travels along the wires to the light bulb where it is converted into heat and light. The switch is used to interrupt the flow of electrical energy to the light bulb.

Although such an electrical system may seem commonplace to us now, it was only invented about 100 years ago. For thousands of years before this, light and heat were obtained by burning oil or some other combustible fuel (e.g., wood). Although the concept of electric charge was known to the ancient Greeks, and electricity as we know it was well-studied in the 19th century, it remained a scientific curiosity for many years until it was put to use in an engineering sense.

In the early part of the 20th century, electrical engineering was concerned with motors, generators and generally large scale electrical machines. In the second half of the 20th century, advances in the understanding of the electronic structure of matter led to the emergence of the new field of electronics. Initially, electronic circuits were built around relatively large scale devices such as thermionic valves. Later, the functionality of valves was implemented using solid-state components through the use of semiconductors.

## 1.2 Electric Charge

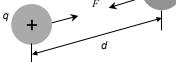

Electrical (and magnetic) effects are a consequence of a property of matter called electric charge. Experiments show that there are two types of charge that we label positive and negative. Experiments also show that

unlike charges attract and like charges repel.

The force of attraction or repulsion can be calculated using Coulomb's law:

• if F is positive, the charges repel;

• if F is negative, the charges attract.

In vector form, the direction of **F** is

The charge on a body usually refers to its excess or net charge. The smallest unit of charge is that on one electron  $q_e = -1.60219 \times 10^{-19}$ coulombs.

$$F = k \frac{q_1 q_2}{d^2}$$

distance between

charges

$$k = \frac{1}{4\pi\varepsilon_o} = 9 \times 10^9 \text{ N m}^2 \text{C}^{-2}$$

$$\varepsilon_o = 8.85 \times 10^{-12}$$

determined by the direction of the unit vector **r** and the farads/metre (F m<sup>-1</sup>) sign of the charges. If the charges have the same sign, then the direction of **F** is the same as that of **r**.  $\mathbf{F} = k \frac{q_1 q_2 \hat{\mathbf{r}}}{d^2}$  The purpose of  $\hat{\mathbf{r}}$  is to point a direction; it has a magnitude of 1.

If the two charges are in some substance, e.g., air, then the **Coulomb force** is reduced. Instead of using  $\varepsilon_0$ , we must use  $\varepsilon$ substance. Often, the relative permittivity substance.  $\varepsilon_r$  is specified.  $\varepsilon_r = \frac{\varepsilon}{\varepsilon_0}$

- 1. imagine that one of the charges is hidden from view:

- 2. the other charge still experiences the Coulomb force and thus we say it is acted upon by an electric field;

- 3. if a test charge experiences a force when placed in a certain place, then an electric field exists at that place. The direction of the field is taken to be that in which a positive test charge would move in the field.

for the Material

$$\varepsilon_r$$

vacuum 1

water 80

glass 8

The units of  $E$  are

newtons/

coulomb

let  $E = k \frac{q_2}{d^2}$ thus  $F = q_1 E$

Note: the origin of the  $F = k \frac{q_1 q_2}{d^2}$  field *E* may be due to the presence of many presence of many charges but the magnitude and direction of the resultant field E can be obtained by measuring the force F on a single test charge q.

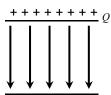

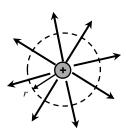

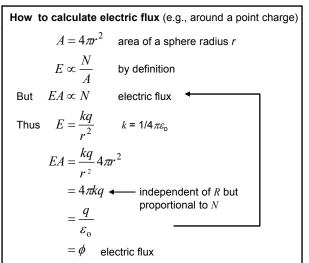

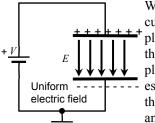

# 1.3 Electric Flux

An electric field may be represented by lines of force. The total number of lines is called the **electric flux**. The number of lines per unit cross-sectional area is the **electric field intensity**, or simply, the magnitude of the electric field.

0

Non-uniform field surrounding a point charge

Uniform electric

field between two

charged parallel

plates

$$E = k \frac{q}{r^2}$$

$$\mathbf{E} = k \frac{q \hat{\mathbf{r}}}{r^2}$$

- Arrows point in the direction of the path taken by a positive test charge placed in the field.

- Number density of lines crossing an area *A* indicates electric field intensity.

- Lines of force start from a positive charge and always terminate on a negative charge (even for an **isolated charge** where the corresponding negative charge may be quite some distance away).

In vector form, the unit vector has a magnitude of 1, but provides direction for the field lines. When q is a positive charge, the electric field E is in the same direction as the unit vector.

Note: for an isolated charge (or charged object) the termination charge is so far away that it contributes little to the field. When the two charges are close together, such as in the parallel plates, both positive and negative charges contribute to the strength of the field. For the plates, O in the formula is the charge on one plate; a factor of 2 has already been included in the formula.

## 1.4 Conductors and Insulators

Atoms consist of a positively charged **nucleus** surrounded by negatively charged **electrons**. Solids consist of a fixed arrangement of atoms usually arranged in a lattice. The position of individual atoms within a solid remains constant because **chemical bonds** hold the atoms in place. The behaviour of the outer electrons of atoms is responsible for the formation of chemical bonds. These outer shell electrons are called **valence electrons**.

#### 1. Conductors

Valence electrons are weakly bound to the atomic lattice and are free to move about from atom to atom.

#### 2. Insulators

Valence electrons are tightly bound to the atomic lattice and are fixed in position.

#### 3. Semiconductors

In **semiconductors**, valence electrons within the crystal structure of the material are not as strongly bound to the atomic lattice and, if given enough energy, may become mobile and free to move just as in a conductor.

valence electrons

shown in these figures

Electrons, especially in conductors, are **mobile charge carriers** (they have a charge, and they are mobile within the atomic lattice).

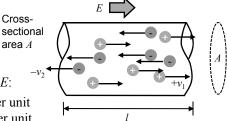

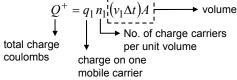

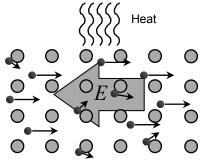

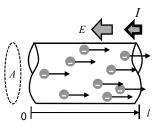

## 1.5 Electric Current

**Mobile charge carriers** may be either positively charged (e.g., positive ions in solution) or negatively charged (e.g., negative ions, loosely bound

valence electrons). Consider the movement during a time  $\Delta t$  of positive and negative charge carriers in a **conductor** of cross-sectional area A and length l placed in an electric field E:

Let there be  $n_1$  positive carriers per unit volume and  $n_2$  negative carriers per unit

volume. Charge carriers move with drift velocities  $v_1$  and  $-v_2$ . In time  $\Delta t$ , each particle moves a distance  $l = v_1 \Delta t$  and  $l = v_2 \Delta t$ .

The total positive charge exiting from the right (and entering from the left) during  $\Delta t$  is thus:

The total negative charge exiting from the left is:  $Q^- = (-q_2)n_2(-v_2\Delta t)A$ The total net movement of charge during  $\Delta t$  is thus:

$Q^{+} + Q^{-} = q_1 n_1 v_1 A \Delta t + (-q_2) n_2 (-v_2) A \Delta t$

The total charge passing any given point in coulombs per second is called electric current:  $Q^+ + Q^-$

$$\frac{Q^{+} + Q}{\Delta t} = q_1 n_1 v_1 A + (-q_2) n_2 (-v_2) A$$

of  $\longrightarrow I = A(q_1 n_1 v_1 + (-q_2) n_2 (-v_2))$

1 amp is the rate of flow of electric charge when one coulomb of electric charge passes a given point in an electric circuit in one second.

Current density J = I/Aamps m<sup>-2</sup> or coulombs m<sup>-2</sup> s<sup>-1</sup>

In general,

$$i = \frac{dq}{dt}$$

Lower case quantities refer to instantaneous values. Upper case refers to steady-state or DC values. In metallic conductors, the mobile charge carriers are negatively charged electrons; hence  $n_1 = 0$ .

Note that the **amp** is a measure of quantity of charge per second and on its own provides no information about the net drift <u>velocity</u> of the charge carriers ( $\approx 0.1 \text{ mm s}^{-1}$ ).

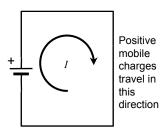

# 1.6 Conventional Current

Electric current involves the net flow of electrical charge carriers, which, in a metallic conductor, are negatively charged electrons. Often in circuit analysis, the physical nature of the actual flow of charge is not important whether it be the flow of free electrons in a wire or the movement of positive ions in a solution.

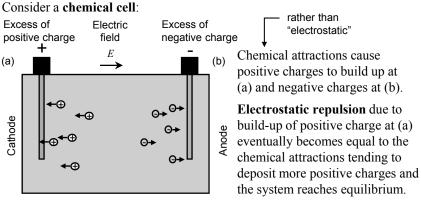

> But, in the 1830s, no one had heard of the **electron**. At that time, Faraday noticed that when current flowed through a wire connected to a chemical cell, one electrode, the **anode**, lost weight and the other electrode, the **cathode**, gained weight. Hence it was concluded that charge carriers, whatever they were, flowed through the wire from the anode to the cathode. The anode was therefore thought to be positively charged with electricity and these electric charges went from the anode to the cathode through the wire.

We now know that the gain and loss of weight at each electrode is due to movement of both positive and negative ions in the solution of the cell rather than movement of charge carriers in the wire and in fact, negatively charged electrons flow from the anode to the cathode along the wire. The anode is charged with electricity all right, but the electric charges there are negative and flow towards the cathode.

For historical reasons, all laws and rules for electric circuits are based on the direction that would be taken by positive charge carriers if they were present, and mobile, in the wire. Thus, in all circuit analysis, *imagine* that current flows due to the motion of positive charge carriers. Current then travels from positive to negative. This is called **conventional current**.

If we need to refer to the actual *physical process* of conduction, then we refer to the specific charge carriers appropriate to the conductor being considered.

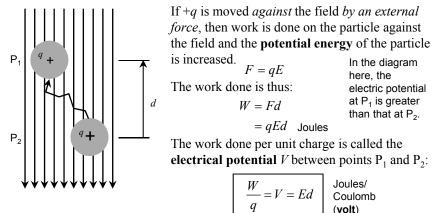

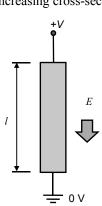

#### 1.7 Potential Difference

When a particle carrying an electric charge is moved from one point  $P_1$  to another  $P_2$  in an electric field, its potential energy is changed since this movement involved a force *F* moving through a distance *d*.

If a charged particle is released in

the field, then work is done by the field on the particle and it acquires **kinetic** energy (= $1/2mv^2$  where v is the velocity acquired after travelling a distance d) and loses potential energy. The force acting on the particle is proportional to the field strength E. The stronger the field, the larger the force – the greater the acceleration and the greater the velocity at distance d.

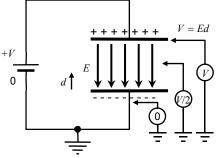

A uniform electric field E exists between two parallel charged plates since a positive test charge placed anywhere within this region will experience a downwards force of the same value. The electric field also represents a

#### potential gradient.

If the negative side of the circuit is grounded (where we set our reference potential to be zero), then the electrical potential at the negative plate is zero and increases uniformly through the space between the plates to the top plate, where it is +V.

The potential gradient (in volts per metre) is numerically equal to the **electric field strength** (newtons per coulomb) but is opposite in direction.

In a *uniform* electric field, the potential decreases uniformly along the field lines and is a potential gradient.

#### 1.8 Resistance

A voltage source, utilising chemical or mechanical means, raises the electrical potential of mobile charge carriers (usually electrons) within it. There is a net build up of charge at the terminals of a voltage source. This net charge results in an **electric field** which is channelled through the conductor. Mobile electrons within the conductor thus experience an electric force and are accelerated.

However, as soon as these electrons move through the conductor, they suffer collisions with other electrons and fixed atoms and lose velocity and thus some of their kinetic energy. Some of the fixed atoms correspondingly acquire **internal energy** (vibrational motion) and the **temperature** of the conductor rises. After collision, electrons are accelerated once more and again suffer more collisions.

Note: negatively charged electrons move in the opposite direction to that of electric field *E*.

Alternate accelerations and decelerations result in a net average velocity of the mobile electrons (called the **drift velocity**) which constitutes an electric current. **Electrical potential energy** is converted into **heat** within the **conductor**. The opposition to the free flow of electrons is called electrical **resistance**.

Experiments show that, for a particular specimen of material, when the applied voltage is increased, the current increases. For most materials, doubling the voltage results in a doubling of the current. That is, the current is directly proportional to the voltage:  $I \propto V$

$$\boxed{\frac{V}{I} = R}$$

Ohm's law

Units: **ohm**  $\Omega$

$$P = VI$$

but

$$V = IR$$

thus

$$P = I^2 R$$

The constant of proportionality is called the **resistance**. Resistance limits the current flow through a material for a particular applied voltage. The rate at which electrical potential energy is converted into heat is the **power** dissipated by the resistor. Since electrical potential is in joules/coulomb, and current is measured in coulombs/second, then the product of voltage and current gives joules/second, which is **power** (in **watts**).

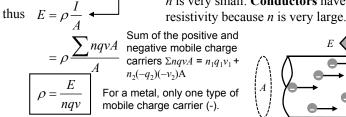

# 1.9 Resistivity

Experiments show that the **resistance** of a particular specimen of material (at a constant temperature) depends on three things:

- the length of the conductor, *l*

- the cross-sectional area of the conductor, A

- the type of material,  $\rho$

The material property which characterises the ability of a particular material to conduct electricity is called the **resistivity**  $\rho$ (the inverse of which is the **conductivity**  $\sigma$ ).

| <b>Material</b> | $\rho$ Ω m @ 20 °C      |

|-----------------|-------------------------|

| silver          | 1.64 × 10 <sup>-8</sup> |

| copper          | 1.72 × 10 <sup>-8</sup> |

| aluminium       | 2.83 × 10 <sup>-8</sup> |

| tungsten        | $5.5	imes10^{-8}$       |

The resistance R (in ohms) of a particular length l of material

of cross-sectional area A is given by:

$\frac{V}{I} = \rho \frac{I}{A}$  The quantity

but  $E = \frac{V}{I}$  the current density J.

I/A is called

Now, V = IR

hence  $=I\frac{\rho l}{\Lambda}$

$$R = \rho \frac{l}{A}$$

The units of  $\rho$  are  $\Omega$  m, the units of  $\sigma$  are S m<sup>-1</sup>.

The number density of mobile charge carriers *n* depends on the material. If the

number density is large, then, if E (and hence v) is held constant, the **resistivity** must be small. Thus, the resistivity depends inversely on n. **Insulators** have a high resistivity since n is very small. **Conductors** have a low resistivity because n is very large.

For a particular specimen of material, n, q, A and l are constants. Increasing the applied field E results in an increase in the **drift velocity** v and hence an increase in current I.

The **resistivity** of a pure substance is lower than that of one containing impurities because the mobile electrons are more likely to travel further and acquire a larger velocity when there is a regular array of stationary atoms in the conductor.

Presence of impurity atoms decreases the average drift velocity.

# 1.10 Variation of Resistance

Consider an applied voltage which generates an electric field E within a conductor of resistance R and of length l and area A.

#### 1. Variation with area

Evidently, if the area A is increased, there will be more mobile charge carriers available to move past a given point during a time  $\Delta t$  under the influence of the field and the current I increases. Thus, for a particular specimen, the resistance decreases with increasing cross-sectional area.

#### 2. Variation with length

Now, the field E acts over a length *l*.

$$V = El$$

If the applied voltage is kept constant, then it is evident that if l is increased, E must decrease. The drift velocity depends on E so that if E decreases, then so does v, and hence so does the current.

#### 3. Variation with temperature

Increasing the **temperature** increases

the random thermal motion of the atoms in the conductor thus increasing the chance of collision with a mobile electron and reducing the average drift velocity and increasing the resistivity. Different materials respond to temperature according to the **temperature coefficient of resistivity**  $\alpha$ .

$$\rho_T = \rho_0 \left[ 1 + \alpha (T - T_0) \right]$$

$$R_T = R_0 \left[ 1 + \alpha (T - T_0) \right]$$

$$R_T = \text{resistance at } T$$

$$R_0 = \text{resistance at } T_0 \text{ (usually 0 °C)}$$

This formula applies to a conductor, not a semi-conductor.

$$Material \qquad \alpha (C^{-1} \Omega^{-1})$$

$$U = \frac{1}{2} \sum_{\alpha \in \mathbb{Z}^{n-1}} \frac{1}{2} \sum_{\alpha \in \mathbb{Z}^{n$$

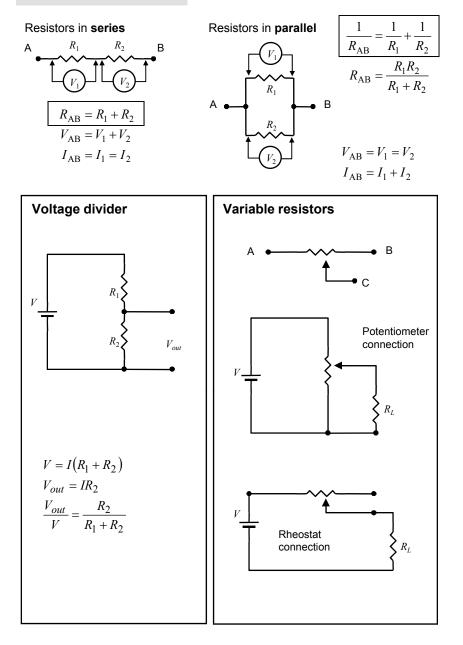

# 1.11 Resistor Circuits

# 1.12 Electromotive Force

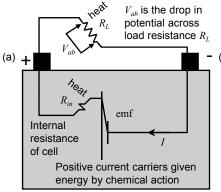

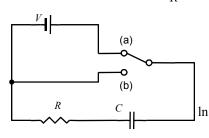

The emf (electromotive force) is defined as the amount of energy expended by the cell in moving 1 coulomb of charge from (b) to (a) within the cell. "Force" is a poor choice of At open-circuit,  $emf = V_{ab}$

words since emf is really "energy" (joules per coulomb).

Now connect an external load  $R_L$  across (a) and (b). The terminal voltage  $V_{ab}$  is now reduced.

The circuit has been drawn to emphasise where potential drops and rises occur.

Loss of positive charge from (a) reduces the accumulated charge at (a) and hence

(b) chemical reactions proceed and more positive charges are shifted from (b) to (a) within the cell to make up for those leaving through the external circuit. Thus, there is a steady flow of positive charge through the cell and through the wire. Assume positive carriers -

conventional current flow.

But, the continuous conversion of chemical potential energy to electrical energy is not 100% efficient. Charge moving within the cell encounters internal resistance, which, in the presence of a current *I*, means a voltage drop so that:

At closed-circuit,  $emf = V_{ab} + IR_{in}$

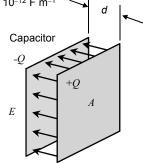

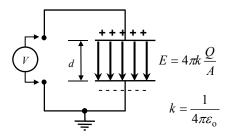

## 1.13 Capacitance

Consider two **parallel plates** across which is placed a voltage V.

When a voltage V is connected across the plates, current begins to flow as charge builds up on each plate. In the diagram, **negative charge** builds up on the lower plate and **positive charge** on the upper plate. The accumulated charge on the two plates establishes an electric field between them. Since there is an electric field between the plates, there is an electrical potential difference between them.

For a **point charge** in space, *E* depends on the distance r away from the charge:  $E = \frac{1}{4\pi\varepsilon_0} \frac{q}{r^2}$ But, for parallel plates holding a total charge O on each plate, calculations show that the electric field *E* in the region between the plates is proportional to the magnitude of the charge *Q* and inversely proportional to the area A of the plates. For a given accumulated charge +O and -Q on each plate, the field E is independent of the distance between the plates.

$$E = \frac{Q}{\varepsilon_0 A}$$

Now,  $V = Ed$

thus  $V = \frac{Q}{\varepsilon_0 A}d$

*Q* in these formulas refers to the charge on ONE plate. Both positive and negative charges contribute to the field E. A factor of 2 has already been included in these formulas.

permittivity of free space = 8.85 × 10<sup>-12</sup> F m<sup>-1</sup>

A charged particle released between the plates will experience an accelerating force.

Capacitance is defined as the ratio of the magnitude of the charge on each plate (+O or -O) to the potential difference between them.

A large capacitor will C =store more charge for every volt across it than a small capacitor.

$$= \frac{Q}{V} \quad \text{but } V =$$

$$= Q \frac{\varepsilon_0 A}{Q d} \quad \text{if the with a set of the se$$

Units: farads

but

$$V = \frac{Q}{\varepsilon A}d$$

space between the plates is filled a dielectric, then capacitance is increased by a factor  $\varepsilon_r$ . A dielectric is an insulator whose atoms become polarised in the electric field. This adds to the storage capacity of the capacitor.  $C = \mathcal{E}_r \mathcal{E}_0 \frac{A}{d}$

#### 1.14 Capacitors

If a capacitor is charged and the voltage source V is then disconnected from it, the accumulated charge remains on the plates of the capacitor.

Since the charges on each plate are opposite, there is an **electrostatic** force of attraction between them but the charges are kept apart by the gap between the plates. In this condition, the capacitor is said to be  $k = \frac{1}{4\pi\varepsilon_0}$  charged. A voltmeter placed across the terminals would read the voltage V used to charge the capacitor.

When a **dielectric** is inserted in a capacitor, the molecules of the dielectric align themselves with the applied field. This alignment causes a field of opposite sign to exist within the material, thus reducing the overall net field. For a given applied voltage, the total net field within the material is small for a material with a high **permittivity**  $\varepsilon$ . The permittivity is thus a measure of how easily the charges within a material line up in the presence of an applied external field. In a conductor, charge carriers not only align but

If the plates are separated by a dielectric, then the field *E* is reduced. Instead of using  $\varepsilon_o$ , we must use  $\varepsilon$  for the substance. Often, the **relative permittivity**  $\varepsilon_r$  is specified.

| $\varepsilon_r = \frac{\varepsilon}{\varepsilon_0}$ | <b>Material</b><br>Vacuum<br>Water<br>Glass | <i>ɛ</i> ,<br>1<br>80<br>8 |

|-----------------------------------------------------|---------------------------------------------|----------------------------|

| 0                                                   | Glass                                       | 8                          |

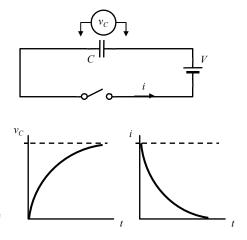

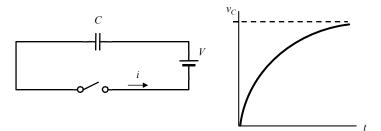

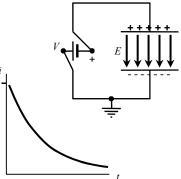

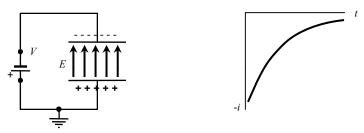

When a capacitor is connected across a voltage source, the current in the circuit is initially very large and then decreases as the capacitor charges. The voltage across the capacitor is initially zero and then rises as the capacitor charges.

In a conductor, charge carriers not only align but actually move under the influence of an applied field. This movement of charge carriers completely cancels the external field. The net electric field within a conductor placed in an external electric field is zero!

# 1.15 Energy Stored in a Capacitor

**Energy** is required to charge a capacitor. When a capacitor is connected across a voltage source, the current in the circuit is initially very large and then decreases as the capacitor charges. The voltage across the capacitor is initially zero and then rises as the capacitor charges.

Energy is expended by the voltage source as it forces charge onto the plates of the capacitor. When fully charged, and disconnected from the voltage source, the voltage across the capacitor remains. The stored electric potential energy within the charged capacitor may be released when desired by discharging the capacitor.

Power

$$P = vi$$

$i = \frac{dq}{dt}$

$Pdt = vdq = dU$

$U = \int_{0}^{Q} vdq$  Energy

$= \int_{0}^{Q} \frac{q}{C}dq$   $C = \frac{q}{v}$

$= \frac{1}{2}\frac{Q^{2}}{C}$   $C = \frac{Q}{V}$

Energy stored

in a capacitor  $U = \frac{1}{2}CV^{2}$

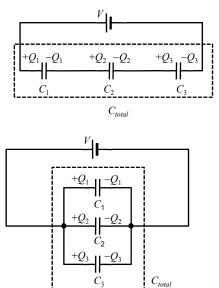

# 1.16 Capacitor Circuits

#### Capacitors in series

$$Q = Q_1 = Q_2 = Q_3$$

$$V = V_1 + V_2 + V_3$$

$$C_{total} = \frac{Q}{V} \quad \text{charge on one plate}$$

$$V_1 = \frac{Q}{C_1}; V_2 = \frac{Q}{C_2}; V_3 = \frac{Q}{C_3}$$

$$V = Q \left(\frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3}\right)$$

$$\frac{1}{C_{total}} = \frac{1}{C_1} + \frac{1}{C_2} + \frac{1}{C_3}$$

Capacitors in parallel

$$\begin{aligned} +Q &= Q_1 + Q_2 + Q_3 \\ V &= V_1 = V_2 = V_3 \\ C_{total} &= \frac{Q}{V} \\ V_1 &= \frac{Q_1}{C_1}; V_2 = \frac{Q_2}{C_2}; V_3 = \frac{Q_3}{C_3} \\ Q &= V_1 C_1 + V_2 C_2 + V_3 C_3 \\ &= V (C_1 + C_2 + C_3) \\ \frac{Q}{V} &= C_1 + C_2 + C_3 \\ &= C_{total} \end{aligned}$$

The combination of capacitors behaves like one large capacitor  $C_{total}$  with charge  $+Q_1$  on one end and  $-Q_3$  at the other end and so  $+Q_1 = +Q_2...$

In this case, the same voltage is applied across all capacitors and since C = Q/V, Q must distribute itself according to C for each capacitor.

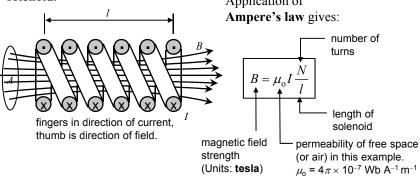

# 1.17 Inductance

In a conductor carrying a steady electric current, there is a magnetic field around the conductor. The magnetic field of a current-carrying conductor may be concentrated by winding the conductor around a tube to form a **solenoid**. Application of

When the current in the coil changes, the resulting change in **magnetic flux** induces an emf in the coil (**Faraday's law**).

emf =

$$-\frac{d\Phi}{dt}$$

magnetic flux

=  $-\mu_0 A \frac{N}{l} \frac{di}{dt}$  where  $B = \frac{\Phi}{A} = \mu_0 I \frac{N}{l}$

magnetic field cross-sectional area of coil

But, this is the emf induced in *each loop* of the coil. Each loop lies within a field *B* and experiences the changing current. The *total* emf induced between the two ends of the coil is thus *N* times that for one loop:

emf =

$$-\left[\mu_0 A \frac{N^2}{l}\right] \frac{di}{dt}$$

The induced emf tends to oppose the change in current (Lenz's law).

Inductance:  $L = \mu_0 A \frac{N^2}{l}$  determines the magnitude of the emf induced within the coil for a given rate of change of current.

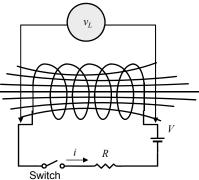

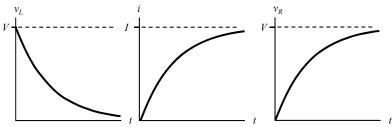

# 1.18 Inductors

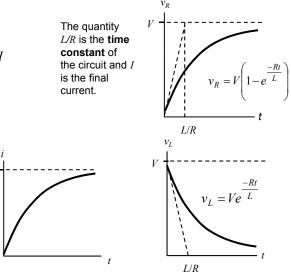

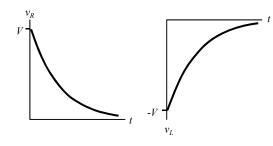

In a circuit with an inductor, when the **switch** closes, a changing current results in a changing magnetic field around the coil. This *changing* magnetic field induces a voltage (emf) in the loops (Faraday's law) which tends to oppose the applied voltage (Lenz's law). Because of the self-induced opposing emf, the current in the circuit does not rise to its final value at the instant the circuit is closed, but grows at a rate which depends on the **inductance** (in **henrys**, L) and resistance (R) of the circuit. As the current increases, the *rate of change* of current decreases and the magnitude of the opposing voltage decreases. The current reaches a maximum value I when the opposing voltage drops to zero and all the voltage appears across the resistance R.

voltage induced by

When the switch is closed, the rate of change of current is controlled by the value of *L* and *R*. Calculations show that the voltage across the inductor is given by: Rt

$$v_I = V e^{-L}$$

the changing current  $v_L = -L \frac{di}{dt}$ The minus sign indicates that if the current is decreasing (*dildt*) rate of change of current through the inductor

the current is decreasing (di/dt is negative) then the voltage  $v_L$  induced in the coil is positive (i.e., same direction as V).

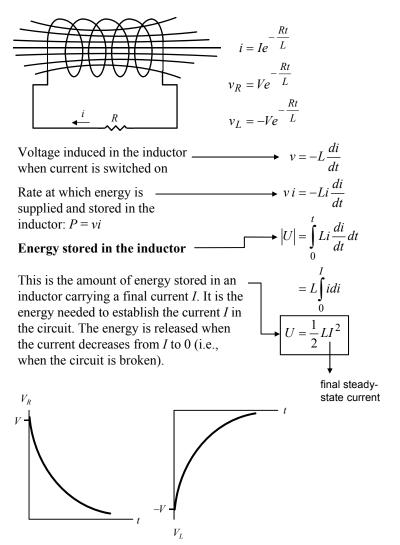

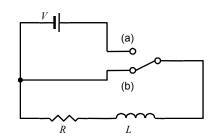

## 1.19 Discharge and Stored Energy

Establishing a current in an inductor requires energy which is stored in the **magnetic field**. When an inductor is discharged, this energy is released. If the inductor is discharged through a resistor as shown, then the rate of decrease in current in the circuit is given by:

#### 1. Electricity

## 1.20 Review Questions

A negative charge of -0.1 μC exerts an attractive force of 0.5 N on an unknown charge at a distance of 0.5 m. Determine the magnitude (and sign) of the unknown charge. (Ans: 138.9 μC)

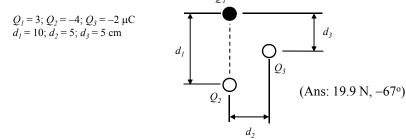

2. Three electrically charged billiard balls are placed at positions as shown in the diagram. Determine the magnitude and direction of the resulting forces on the black ball.  $Q_I$

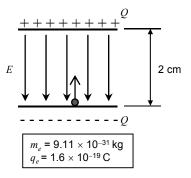

3. A uniform electric field exists between two oppositely charged parallel plates. An electron is released from rest at the surface of the negatively charged plate and strikes the surface of the positively Echarged plate. The distance between the plates is 2 cm and it takes  $1.5 \times 10^{-8}$ seconds for the electron to travel from one plate to the other. (a) Find the electric field strength, and (b) the velocity of the electron as it strikes the positively charged plate.

(Ans: 1012 NC<sup>-1</sup>,  $2.67 \times 10^{6} \text{ ms}^{-1}$ )

4. A steady current of 6 A is maintained in a metallic conductor. What charge (in coulombs) is transferred through it in 1 minute?

(Ans: 360 C)

Two parallel plates are 1 cm apart and are connected to a 500 V source. What force will be exerted on a single electron half way between the plates? (Ans: 8 × 10<sup>-15</sup> N)

6. Calculate the resistance of 100 m of copper wire which has a diameter of 0.6 mm.

(Ans:  $6.08 \Omega$ )

- 7. A steady voltage source V = 1 V is connected to a coil which consists of a 50 m length of copper wire of radius 0.01 mm. Given that the number density of mobile electrons in copper is  $8.5 \times 10^{22}$  cm<sup>-3</sup> and  $\rho = 1.72 \times 10^{-8} \Omega$  m, calculate:

- (a) the electric field *E* which acts on the mobile electrons in the coil.

- (b) the drift velocity v of the mobile electrons.

- (c) the resistance *R* of the coil.

- (d) the steady DC current *I* in the coil.

(Ans:  $0.02 \text{ V m}^{-1}$ ;  $8.6 \times 10^{-5} \text{ m s}^{-1}$ ; 2738 W; 0.36 mA)

8. A fuse in a motor vehicle electrical system has a resistance of  $0.05 \Omega$ . It is designed to blow when the power dissipation exceeds 50 W. What is the current rating of the fuse?

(Ans: 31.6 A)

9. A 12 volt battery in a motor vehicle is capable of supplying the starter motor with 150 A. It is noticed that the terminal voltage of the battery drops to 10 V when the engine is cranked over with the starter motor. Determine the internal resistance of the 12 volt battery.

(Ans:  $0.013 \Omega$ )

- 10. A capacitor consists of two parallel plates each of area 200 cm<sup>2</sup> separated by an air gap of 0.4 mm thickness. 500 V is applied. Calculate:

- (a) capacitance of this capacitor;

- (b) charge on each plate;

- (c) energy stored in the capacitor;

- (d) electric field strength between the plates.

(Ans: 442 pF,  $2.24 \times 10^{-7}\,C,\, 5.6 \times 10^{-5}\,J,\, 1.25 \times 10^{6}\,V\,m^{-1})$

A coil has an inductance of 5 H and a resistance of 20 Ω. If a DC voltage of 100 V is applied to the coil, find the energy stored in the coil when a steady maximum current has been reached. (Ans: 62.5 J)

# 2. DC Circuits

60 Ω

**20** Ω

9 V

## 2.1 Superposition

In a circuit containing several sources of emf, the current flowing in any branch of the circuit will be equal to the sum of the **current components** that would flow in the branch if each source of emf were to be acting alone.

6 V

Example:

Find the current in the 20  $\Omega$  resistor in the circuit shown.

Solution:

We proceed as follows: replace all sources with their **internal**

**resistances** except one and calculate the current component flowing in the branch of interest by combining resistors in serial or parallel as required.

1. Combine 60 and  $20 \Omega$  into one resistance.

2. Analyse for unknown current *component*.

$$R_{60,20} = \left(\frac{1}{20} + \frac{1}{60}\right)^{-1}$$

= 15 \Omega

$$R_T = 15 + 30$$

= 45

$$I_1 = \frac{6}{45}$$

= 0.133 \A

$$V_{ab} = (0.133)(15)$$

= 1.995 \V

$$I_2 = \frac{1.995}{20}$$

= 0.1 \A

3 V

**30** Ω

$$R_{60,30} = 20 \Omega$$

$$R_T = 20 + 20$$

$$= 40 \Omega$$

$$I_2 = \frac{3}{40}$$

$$= 0.075 \text{ A}$$

$$R_{30,20} = 12 \Omega$$

$$R_T = 72 \Omega$$

$$I_3 = \frac{9}{72}$$

$$= 0.125 \text{ A}$$

$$V_{ab} = 0.125(12)$$

$$= 1.5 \text{ V}$$

$$I_2 = \frac{1.5}{20}$$

$$= 0.075 \text{ A}$$

4. Add current components together for final answer.

$$I_{total} = 0.1 + 0.075 + 0.075$$

$$= 0.25 \text{ A}$$

#### 2. DC Circuits

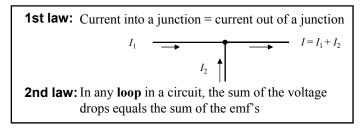

### 2.2 Kirchhoff's Laws

Solution:

- 1. Divide the circuit up into **current loops** and draw an arrow which indicates the direction of current assigned to each loop (the direction you choose need not be the correct one. If you guess wrongly, then the current will simply come out negative in the calculations).

- 2. Consider each loop separately:

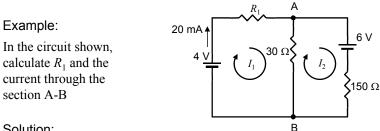

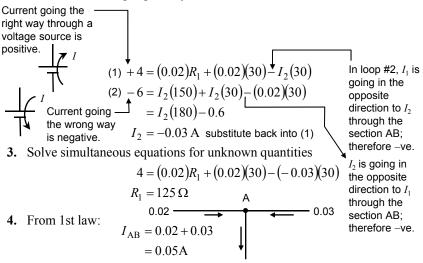

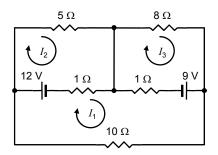

## 2.3 Kirchhoff's Laws Example

Determine the current in the two 1  $\Omega$  resistors in the following circuit.

0

0

1

0

0

1

0

(1)

$$-12 + 9 = I_1(10 + 1 + 1) + -I_2(1) - I_3(1)$$

$-3 = 12I_1 - I_2 - I_3$

(2)  $12 = I_2(5+1) - I_1(1)$

(3)  $-9 = I_3(8+1) - I_1(1)$

Three simultaneous equations. Solve by matrix method to give:

$$I_1 = -0.170 \text{ A}$$

$I_2 = 1.972 \text{ A}$

$I_3 = -1.019 \text{ A}$

Thus:

$$I_2 - I_1 = 1.972 - 0.170$$

= 2.142 A  $\leftarrow$

$I_1 - I_3 = -0.170 - -1.019$

= 0.849 A  $\rightarrow$

The minus signs indicate that the currents  $I_1$  and  $I_3$  are opposite in direction to that shown in the diagram above.

Arrange coefficients in this format. The aim is to obtain a pattern of 0's and 12 -1 -1 -3 1's on the left to give the 0 12 -1 6 value of the unknown -1 0 9 -9 values on the right by manipulating rows (R). 1 0 | -12 |-6 Swap R1, R2 and multiply 12 -1| -3-1 new R1 by -1 -1 0 9 -9 0 - 121 -6 Add  $-12 \times R1$  to R2 71 -1 141 Add R1 to R3 -6 9 -21 -6 0 -12 Divide R2 by 71 -0.014 1.986 1 -21 -6 9 0 -0.084 -0.084 Add  $6 \times R2$  to R1 1 -0.014 1.986 Add  $6 \times R2$  to R3 0 0 8.916 -9.084  $|1 \quad 0 \quad 0 \quad |-0.170| \longleftarrow I_1$  Divide R3 by 8.916 0 1 0 1.972 🗲  $-I_2$  Add 0.014  $\times$  R3 to R2  $-I_3$  Add 0.084 × R3 to R1 0 0 1 -1.019

### 2. DC Circuits

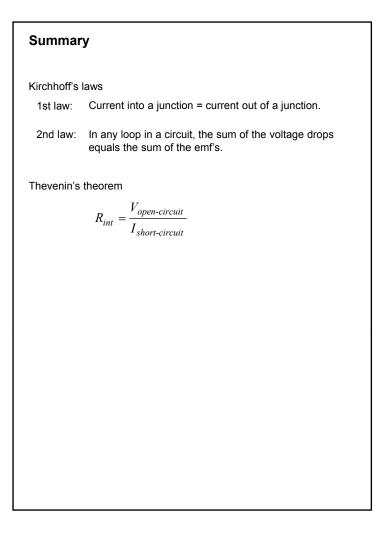

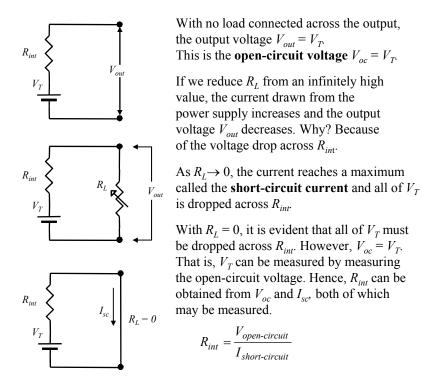

# 2.4 Thevenin's Theorem

Consider a voltage source  $V_T$  with internal resistance  $R_{int}$ .

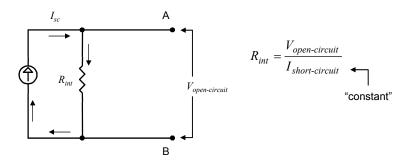

$V_T$  and  $R_{int}$  are useful tools for reducing a complicated power supply circuit to a simpler circuit. This is Thevenin's theorem. That is, any **two-terminal voltage source**, no matter how complicated, can be represented by  $V_T$  and  $R_{inr}$

| Analysis                                                                                                                          | Measurement                                                                |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| 1. Calculate open-circuit voltage $V_T$ using Kirchhoff or superposition                                                          | <ol> <li>Or, measure short-circuit<br/>current and open-circuit</li> </ol> |  |

| 2. Determine $R_{int}$ by replacing all internal voltage sources with their internal resistances and analysing resistance network | voltage with multimeter to obtain <i>R<sub>int</sub></i>                   |  |

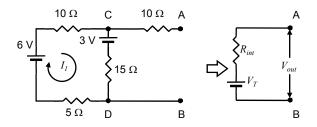

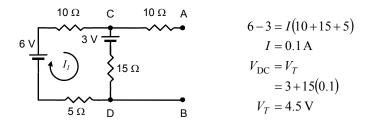

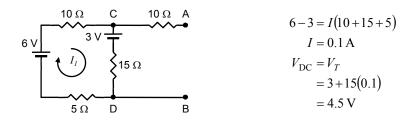

### 2.5 Thevenin's Theorem Example

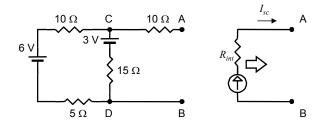

Reduce this circuit to a single voltage source  $V_T$  and internal resistance  $R_{int}$ .

(1) Determine  $V_T$  by calculating **open-circuit voltage** using Kirchhoff or superposition.

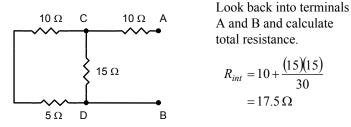

(2) Determine  $R_{int}$  by replacing all emf's with their **internal resistances** (zero in this example).

(3) Calculate short-circuit current if desired.

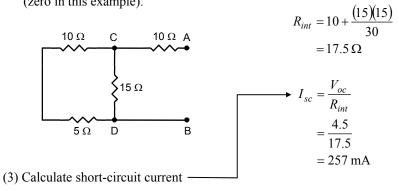

$$I_{sc} = \frac{V_{oc}}{R_{int}} = \frac{4.5}{17.5} = 257 \text{ mA}$$

#### 2. DC Circuits

### 2.6 Norton's Theorem

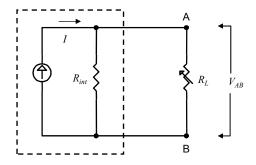

Imagine a black box contains a special generator that produces a completely variable voltage but always produces a **constant current** *I* (equal to the **short-circuit current**).

*I* is a constant.  $V_{AB}$  varies as  $R_L$  varies.

$R_{int}$  must be in parallel with the power source so that *I* remains constant when  $R_L \rightarrow$  infinity. When  $R_L = 0$ ,  $I = I_{sc} =$ constant.

Consider open-circuit conditions:

Circuits (or parts thereof) may be reduced to **equivalent circuits** in terms of either **constant voltage** (Thevenin) or **constant current** (Norton) sources with an internal resistance. We shall see shortly that Thevenin and Norton equivalent circuits are exactly the same thing from the point of view of the voltage and current seen by an external load.

## 2.7 Norton's Theorem Example

Reduce this circuit to a constant current source  $I_{sc}$  with a parallel internal resistance  $R_{inr}$

(1) Determine the open-circuit voltage by Kirchhoff or superposition.

(2) Determine  $R_{int}$  by replacing all emf's with their internal resistances (zero in this example).

#### 2. DC Circuits

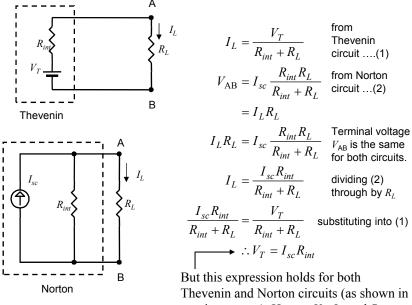

### 2.8 Equivalence of Norton and Thevenin

Consider these two representations of a **two-terminal power supply**. If both of these can replace the actual circuitry of the power supply and appear to be the same from the point of view of whatever is connected to the output terminals A and B, then the terminal voltage  $V_{AB}$  and load current  $I_L$  must be the same for each circuit.

previous pages). Hence,  $V_T$ ,  $I_{sc}$  and  $R_{int}$  are exactly the same for each circuit.

#### Equivalence of Norton and Thevenin

Thevenin and Norton equivalent circuits are two different ways of representing a complicated circuit, either as a simple series or a simple parallel circuit. Which one do we use? It depends on the circuit being analysed. For transistor circuits, the Norton equivalent circuit is better and leads to a simpler analysis because transistors are mostly current controlling devices.

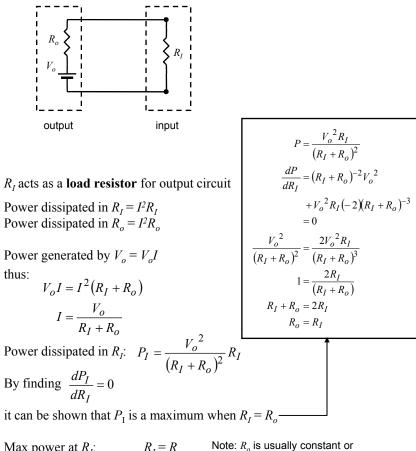

## 2.9 Maximum Power Transfer

Transfer from an output device (e.g., amplifier) to an input device (e.g., loudspeaker)

Max power at  $R_I$ : $R_I = R_o$ Max voltage drop  $R_I$ : $R_I >> R_o$ Max current at  $R_I$ : $R_I << R_o$

Note:  $R_o$  is usually constant o fixed by the apparatus.

### 2. DC Circuits

# 2.10 Review Questions

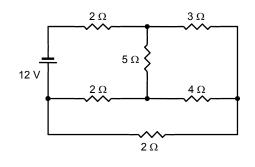

1. Using Kirchhoff's laws, find the current in the 4  $\Omega$  resistor in the network below:

(Ans: 0.122 A)

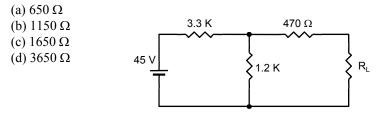

2. Find the current through the load resistor  $R_L$  when it takes the following values:

Hint: use Thevenin's theorem.

(Ans: 6, 4.8, 4, 2.4 mA)

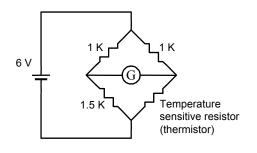

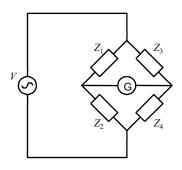

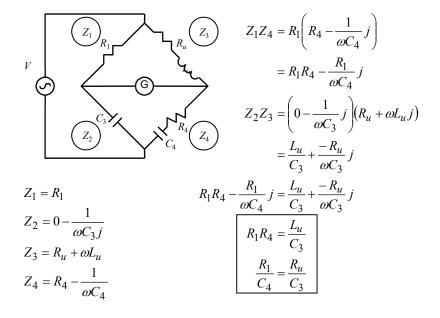

3. A Wheatstone's bridge is used to measure temperature with the aid of a temperature sensitive resistor (a thermistor). If the meter (G) across the bridge has a resistance of 1200  $\Omega$ , and the resistance of the thermistor changes from 1500  $\Omega$  to 1600  $\Omega$  for a change in temperature of 60 °C to 61 °C, determine the change in current through the meter.

(Ans: 0.038 mA)

# 3. AC Circuits

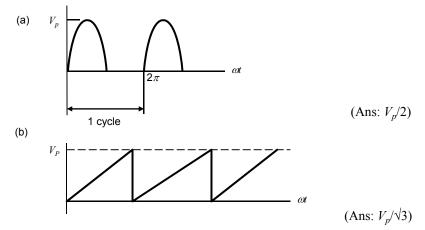

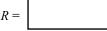

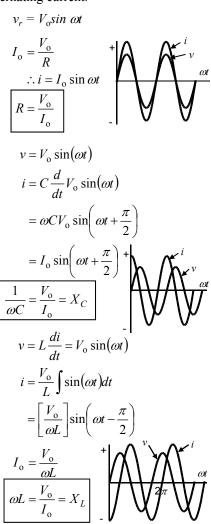

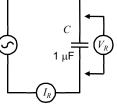

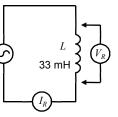

| Summary                                                                         |                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

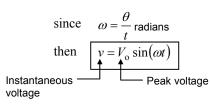

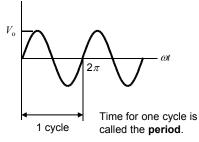

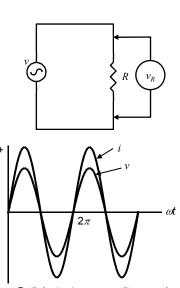

| $v = V_p \sin(\omega t)$                                                        | Instantaneous voltage                                                                                                             |  |  |

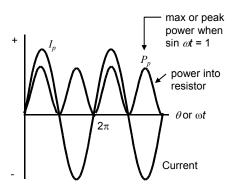

| $V_{rms} = \frac{V_p}{\sqrt{2}} = 0.707 V_p$                                    | rms voltage                                                                                                                       |  |  |

| $I_{rms} = \frac{I_p}{\sqrt{2}} = 0.707 I_p$                                    | rms current                                                                                                                       |  |  |

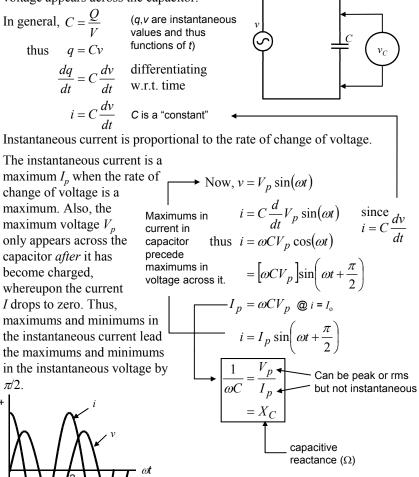

| $X_C = \frac{1}{\omega C}$                                                      | Capacitive reactance                                                                                                              |  |  |

| $X_L = \omega L$                                                                | Inductive reactance                                                                                                               |  |  |

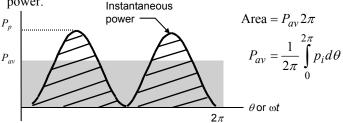

| $P_R = V_{rms} I_{rms}$                                                         | Reactive power                                                                                                                    |  |  |

| $P_{av} = V_{rms} I_{rms} \cos \phi$                                            | Average (active) power                                                                                                            |  |  |

| $S = V_{rms}I_{rms}$                                                            | Apparent power                                                                                                                    |  |  |

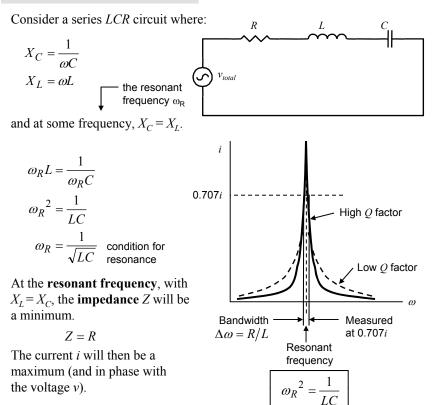

| $ Z  = \sqrt{R^2 + (X_L - X_C)}$ $\tan \phi = \left[\frac{X_L - X_C}{R}\right]$ | $\overline{\big)^2} \qquad Z = R + j \big( X_L - X_C \big)$<br>Impedance<br>$= R + j \bigg( \omega L - \frac{1}{\omega C} \bigg)$ |  |  |

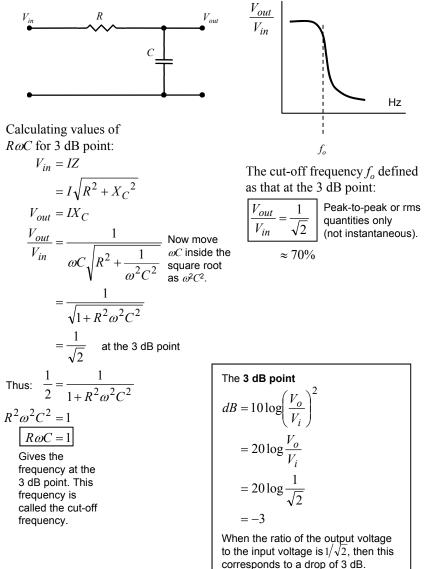

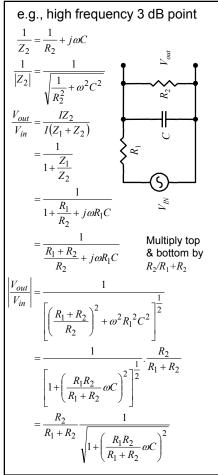

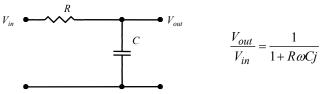

| $\frac{V_{out}}{V_{in}} = \frac{1}{\sqrt{1 + R^2 \omega^2 C^2}}$                | Low-pass filter                                                                                                                   |  |  |

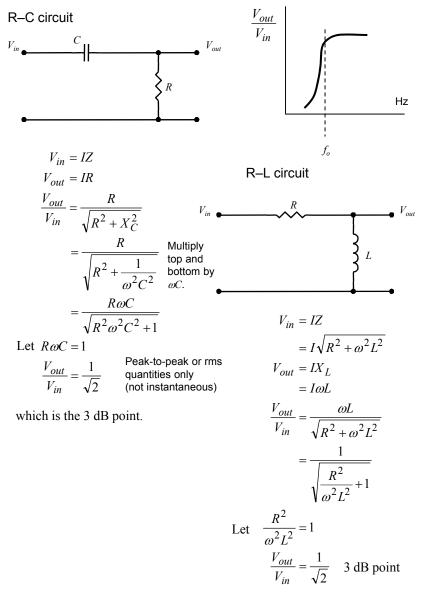

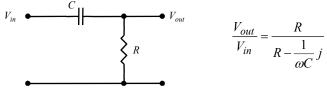

| $\frac{V_{out}}{V_{in}} = \frac{R\omega C}{\sqrt{R^2 \omega^2 C^2 + 1}}$        | High-pass filter                                                                                                                  |  |  |

| $R\omega C = 1$                                                                 | 3 dB point                                                                                                                        |  |  |

# 3.1 AC Voltage

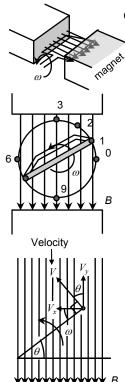

Consider a conductor at constant angular speed ( $\omega$ ):

- at (0) motion of conductor is parallel to *B*, hence induced voltage = 0;

- at (1), conductor has begun to cut magnetic field lines *B*, hence some voltage is induced;

- at (2), conductor cuts magnetic field lines at a greater rate than (1) and thus a greater voltage is induced;

- at (3), conductor cuts magnetic field lines at maximum rate, thus maximum voltage is induced;

- from (3) to (6), the rate of cutting becomes less;

- at (6), conductor moves parallel to B and v = 0;

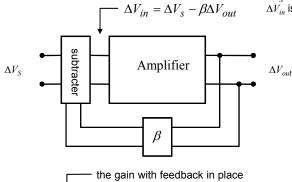

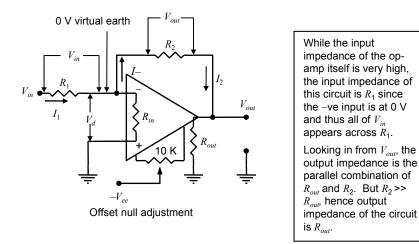

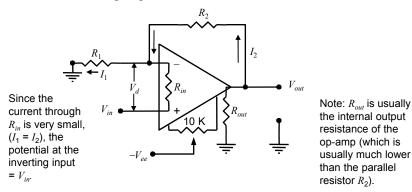

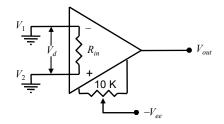

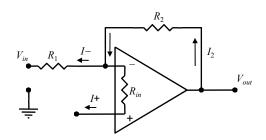

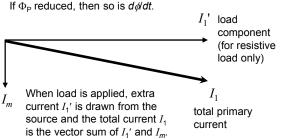

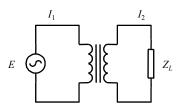

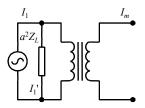

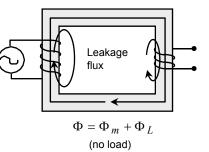

- from (6) to (9), conductor begins to cut field lines again but in the opposite direction, hence induced voltage is reversed in polarity.